## Architecture des ordinateurs

Jeremy Fix

$27\ {\rm septembre}\ 2025$

Ce support de cours a été réalisé, notamment, grâce aux outils suivants :

- Latex/TeXLive 2013 (https://www.tug.org/texlive/)

- GNU Emacs (https://www.gnu.org/software/emacs/) et l'extension Flyspell (http://www-sop.inria.fr/members/Manuel.Serrano/flyspell/flyspell.html)

- Ubuntu 14.04 (http://www.ubuntu.com/)

- inkscape (https://inkscape.org), ipe 7.1.8 (http://ipe.otfried.org/), tikz (http://pgf.sourceforge.net/), l'extension circuitikz (http://www.ctan.org/tex-archive/graphics/pgf/contrib/circuitikz), l'extension tikz-timing (https://www.ctan.org/pkg/tikz-timing)

- logisim (version originale: http://www.cburch.com/logisim/index.html, fork utilisé ici: https://github.com/lawrancej/logisim)

- une machine à café

Ce support de cours est accompagné de sujets de TP réalisés sous logisim. Les sujet sont disponibles à l'adresse http://malis.metz.supelec.fr/~fix\_jer.

# Table des matières

| 1        | Coc | dages et | opérations binaires 1                                                          |

|----------|-----|----------|--------------------------------------------------------------------------------|

|          | 1.1 | Représe  | entation des entiers naturels                                                  |

|          |     | 1.1.1    | Représentation en base p                                                       |

|          |     | 1.1.2    | Représentation binaire, p=2                                                    |

|          |     | 1.1.3    | Représentation hexadécimale, p=16                                              |

|          |     | 1.1.4    | Raccourcis de conversion binaire/hexadécimal                                   |

|          |     | 1.1.5    | Codage Binary Coded Décimal et Codage de Gray                                  |

|          | 1.2 | Opérati  | ions arithmétiques sur les représentations non signées                         |

|          | 1.3 | Représe  | entations et opérations avec un nombre fixé de bits                            |

|          | 1.4 | Représe  | entation des entiers relatifs                                                  |

|          |     | 1.4.1    | Complément réduit et complément vrai                                           |

|          | 1.5 | Opérati  | ions arithmétiques sur les représentations signées                             |

|          |     | 1.5.1    | Additions/Soustractions                                                        |

|          | 1.6 | Représe  | entation des nombres réels : virgule fixe et virgule flottante                 |

|          |     | 1.6.1    | Représentation par virgule fixe (fixed-point)                                  |

|          |     | 1.6.2    | Représentation par virgule flottante (floating-point)                          |

|          |     | 1.6.3    | Exemple de la représentation en virgule flottante binary-16                    |

|          | 1.7 | Représe  | entation des caractères                                                        |

|          | 1.8 | Un exe   | mple                                                                           |

| <b>2</b> | La  | couche   | physique et la couche logique 17                                               |

|          | 2.1 | Un peu   | d'électronique                                                                 |

|          |     | 2.1.1    | Niveaux logiques et valeurs de tension                                         |

|          |     | 2.1.2    | Transistors CMOS et inverseur                                                  |

|          |     | 2.1.3    | Portes NAND et NOR à deux entrées                                              |

|          |     | 2.1.4    | Autres portes à une ou deux entrées                                            |

|          |     | 2.1.5    | Table de vérité et synthèse de circuit logique                                 |

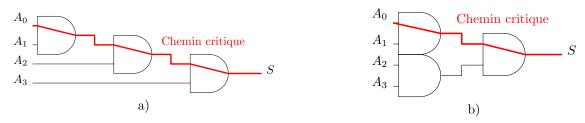

|          |     | 2.1.6    | Temps de propagation et notion de chemin critique                              |

|          | 2.2 |          | s de logique combinatoire                                                      |

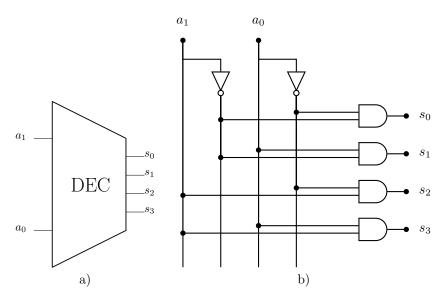

|          |     | 2.2.1    | Décodeur                                                                       |

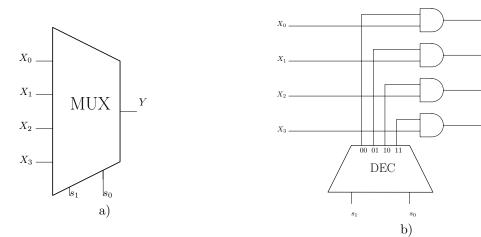

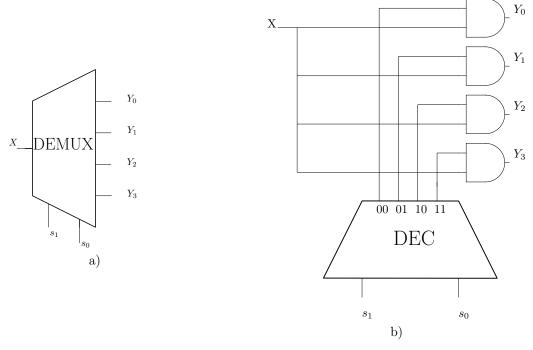

|          |     | 2.2.2    | Multiplexeur / démultiplexeur                                                  |

|          |     | 2.2.3    | Aléa statique                                                                  |

|          |     | 2.2.4    | Mutiplexeur : universalité et mémoire en lecture seule (ROM)                   |

|          |     | 2.2.5    | Unité arithmétique et logique pour les entiers                                 |

|          |     | 2.2.6    | Unité arithmétique en virgule flottante                                        |

|          | 2.3 | Circuits | s de logique séquentielle                                                      |

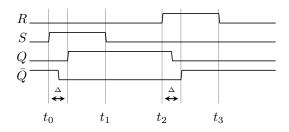

|          |     | 2.3.1    | Verrou/Bascule RS                                                              |

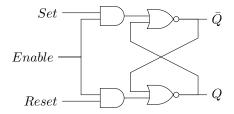

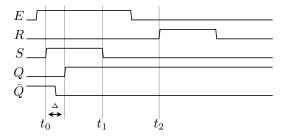

|          |     | 2.3.2    | Verrou D                                                                       |

|          |     | 2.3.3    | Systèmes logiques synchrones : horloge et fronts montants                      |

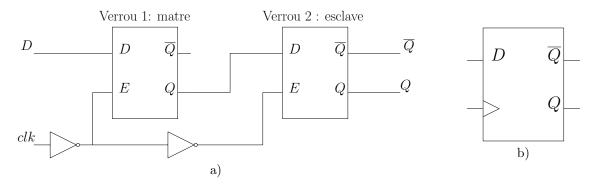

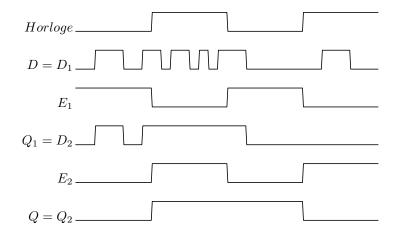

|          |     |          | Bascule D synchrone sur front montant : maître esclave                         |

|          |     |          | Réalisation d'un verrou D avec un mutliplexeur                                 |

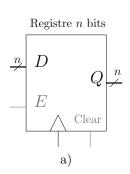

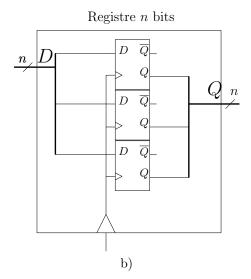

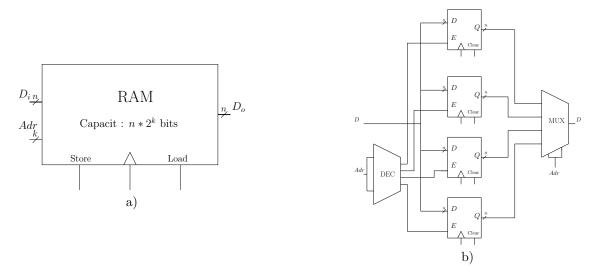

|          |     | 2.3.6    | Registre et mémoire RAM (Random Access Memory)                                 |

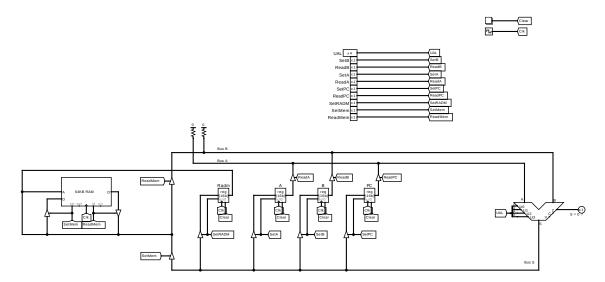

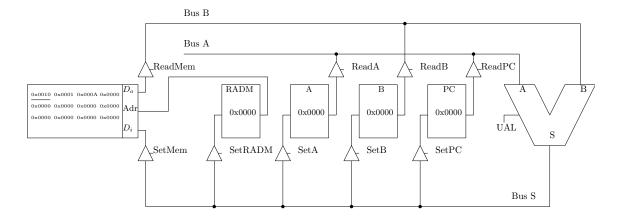

|          | 2.4 |          | emière architecture interne simple d'un microprocesseur                        |

|          |     |          | Registres internes: accumulateurs, registre d'adresse et compteur ordinal . 43 |

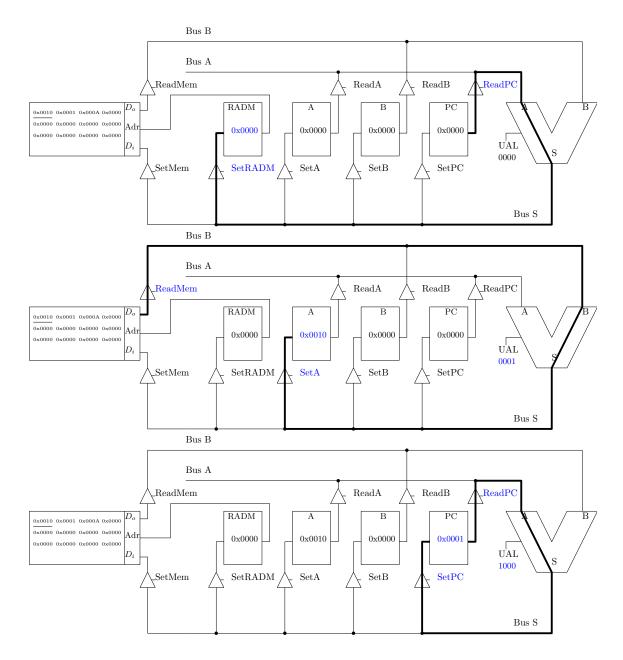

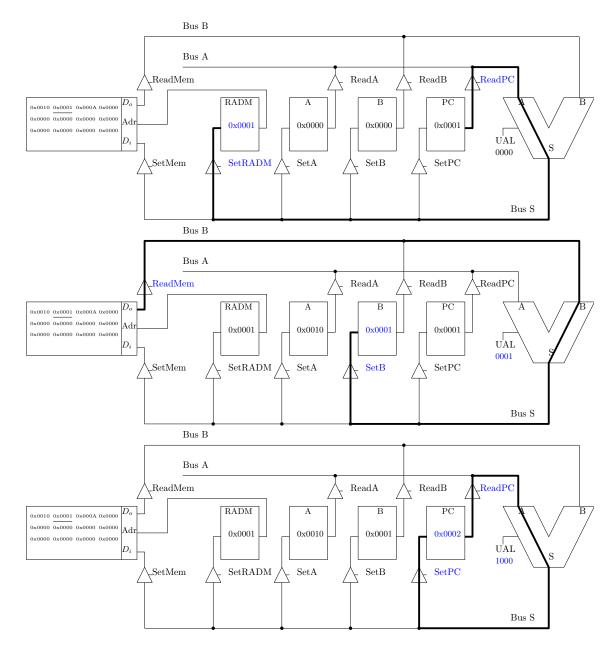

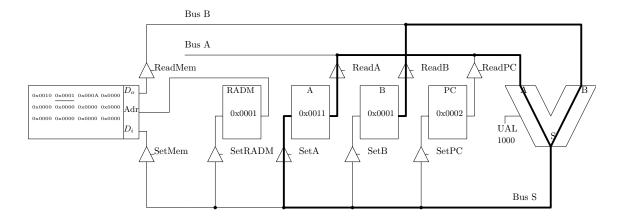

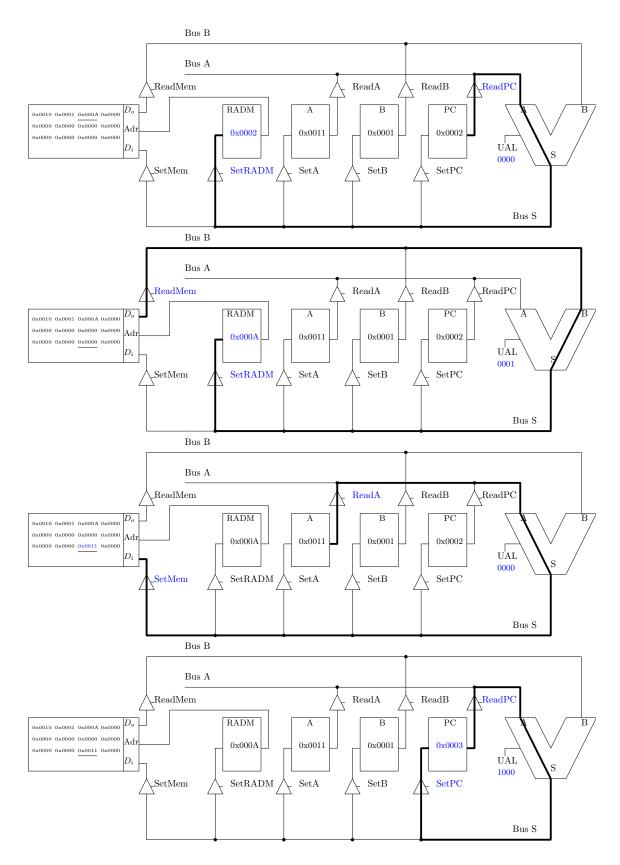

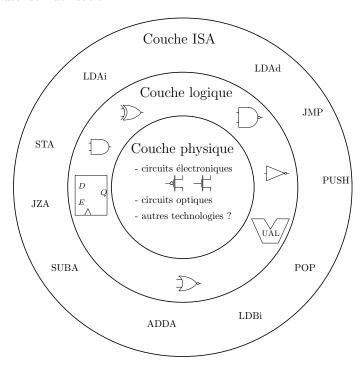

|   |            | 2.4.2<br>2.4.3 | Séquencement du chemin de données       4         Exemple       4               |

|---|------------|----------------|---------------------------------------------------------------------------------|

| 3 | La c       | couche         | ISA 5                                                                           |

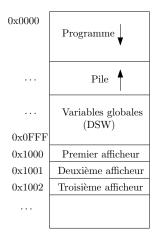

|   | 3.1        | Progra         | amme et données en mémoire                                                      |

|   |            | 3.1.1          | Codage des instructions en mémoire                                              |

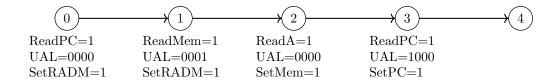

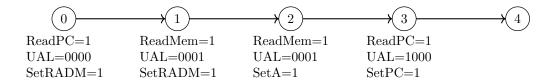

|   |            | 3.1.2          | Récupérer l'instruction depuis la mémoire (fetch)                               |

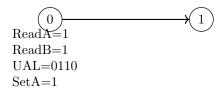

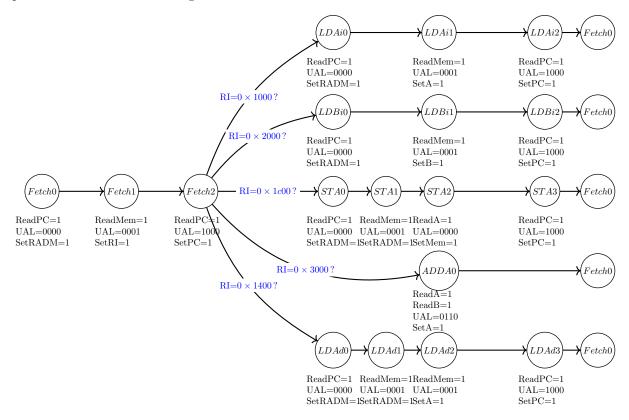

|   | 3.2        | Génér          | er les micro-instructions par une machine à états finis                         |

|   |            | 3.2.1          | Une machine à états finis pour le fetch                                         |

|   |            | 3.2.2          | Une machine à états finis par instruction                                       |

|   |            | 3.2.3          | Une machine à états finis pour toutes les instructions                          |

|   | 3.3        | Séque          | ncement microprogrammé du chemin de données                                     |

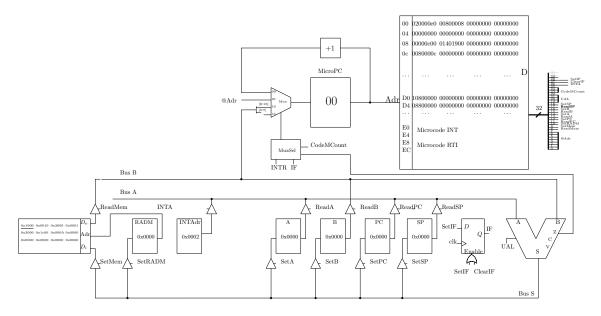

|   |            | 3.3.1          | Circuit logique du séquenceur microprogrammé et interface avec le chemin        |

|   |            | 0.0.2          | de données                                                                      |

|   |            | 3.3.2          | Les branchements                                                                |

|   | 3.4        |                | itulons                                                                         |

|   | 0.1        | 3.4.1          | Architecture                                                                    |

|   |            | 3.4.2          | Liste et format des instructions                                                |

|   |            | 9.4.2          | Liste et format des instructions                                                |

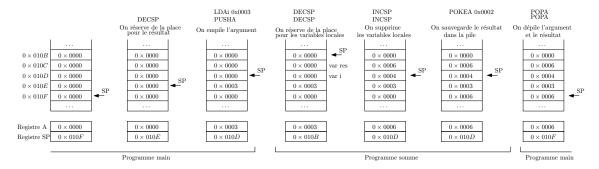

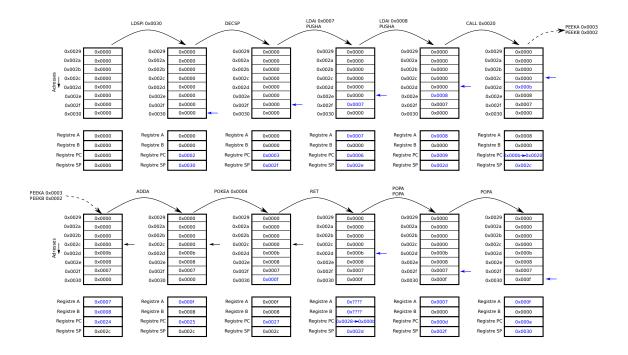

| 4 | Pro        | cédure         | es, pile et pointeur de pile                                                    |

|   | 4.1        | Motiv          | ation                                                                           |

|   | 4.2        | La pil         | e : modification du chemin de données et nouvelles instructions                 |

|   | 4.3        | -              | e pour passer des arguments et récupérer des résultats                          |

|   | 4.4        | -              | et retour de routines                                                           |

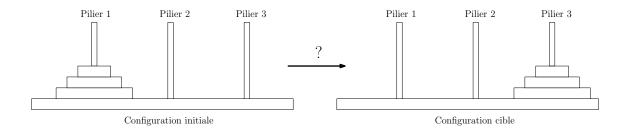

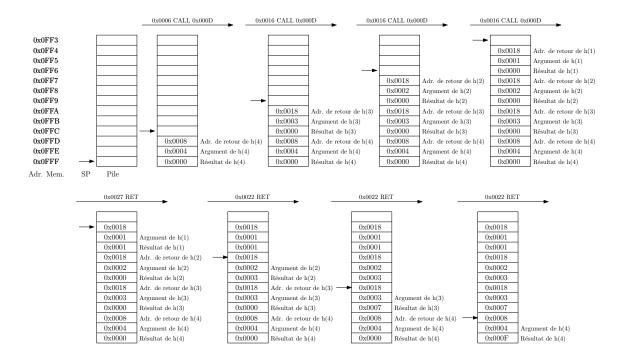

|   | 4.5        |                | ple : nombre de mouvements pour résoudre les tours de Hanoï                     |

|   | 1.0        |                | por inomotio de inodificio podr regoldare les todas de rivido i i i i i i i i i |

| 5 | Tra        | ductio         | n, Compilation, interprétation                                                  |

|   | 5.1        | Langa          | ge bas niveau : Assembleur                                                      |

|   |            | 5.1.1          | Quelques éléments de syntaxe de notre langage d'assemblage 8                    |

|   |            | 5.1.2          | L'assembleur                                                                    |

|   | 5.2        | Langa          | ge de haut niveau                                                               |

|   |            | 5.2.1          | Quelques éléments de langages de haut niveau                                    |

|   |            | 5.2.2          | Interprété ou compilé                                                           |

|   | 5.3        | Comp           | ilateur                                                                         |

|   |            | 5.3.1          |                                                                                 |

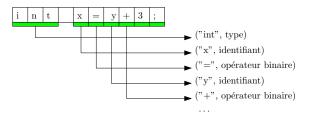

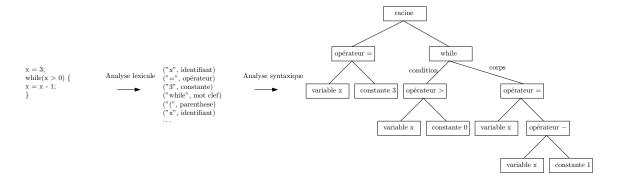

|   |            | 5.3.2          | La phase d'analyse (frontend)                                                   |

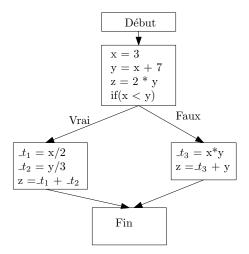

|   |            | 5.3.3          | Génération et optimisation d'une représentation intermédiaire                   |

|   |            | 5.3.4          | La phase de synthèse                                                            |

|   |            | 0.0.4          | La phase de synthèse                                                            |

| 6 | Laı        | mémoi          | re 9                                                                            |

|   | 6.1        | Les di         | fférentes formes de mémoire                                                     |

|   |            | 6.1.1          | Mémoire morte (ROM)                                                             |

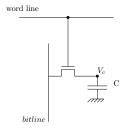

|   |            | 6.1.2          | Mémoire vive (RAM)                                                              |

|   |            | 6.1.3          | Mémoire de masse : disque dur                                                   |

|   |            | 6.1.4          | Synthèse des mémoires en lecture/écriture : vive et de masse                    |

|   | 6.2        |                | chie de mémoire                                                                 |

|   | 0.2        |                |                                                                                 |

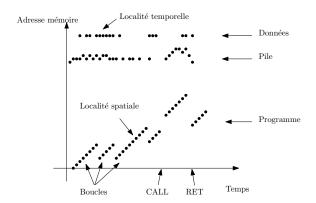

|   |            | 6.2.1          | Principe de localité spatiale et temporelle                                     |

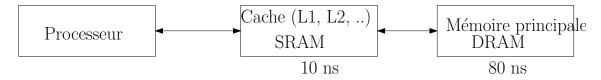

|   | <i>c</i> o | 6.2.2          | Structure hierarchique de la mémoire : le meilleur des deux mondes 9            |

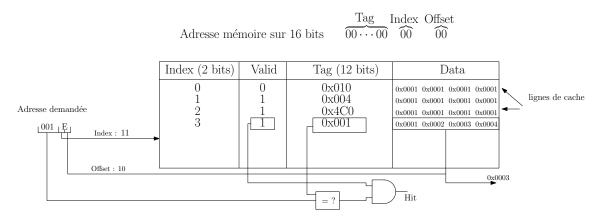

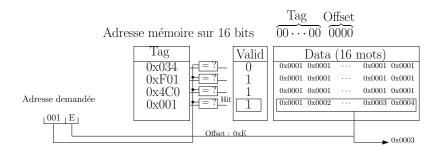

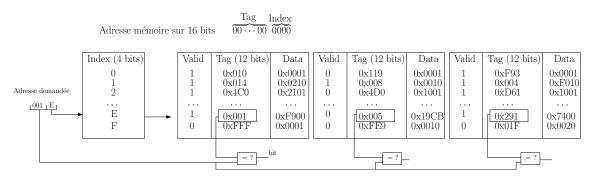

|   | 6.3        |                | ire cache                                                                       |

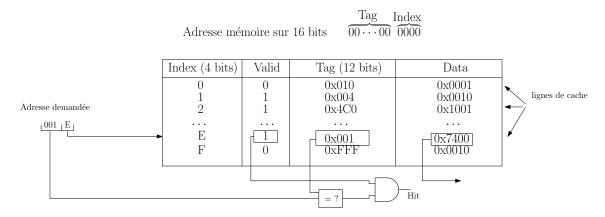

|   |            | 6.3.1          | Cache à correspondance directe                                                  |

|   |            | 6.3.2          | Cache associatif                                                                |

|   |            | 6.3.3          | Cache associatif à n entrées                                                    |

|   |            | 6.3.4          | Cohérence du cache et de la mémoire centrale                                    |

TABLE DES MATIÈRES

Bibliographie

| 7            | $\mathbf{Les}$ | périphériques et leur gestion par interruption                       | 103 |

|--------------|----------------|----------------------------------------------------------------------|-----|

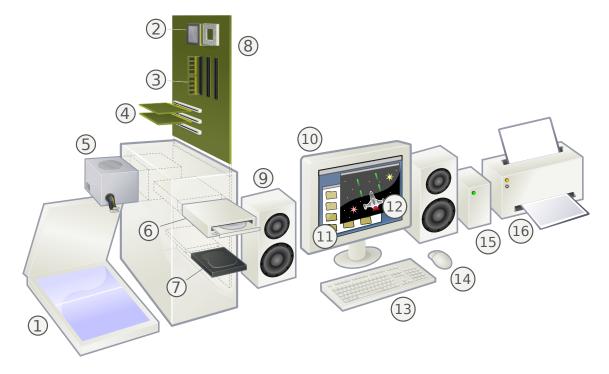

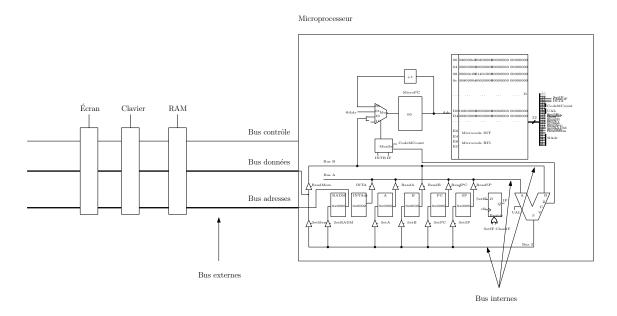

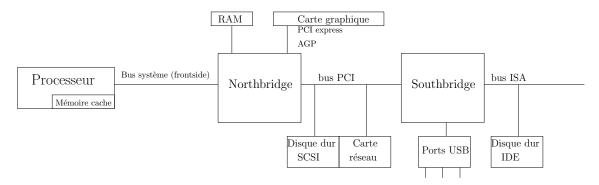

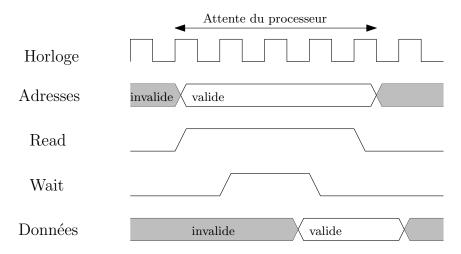

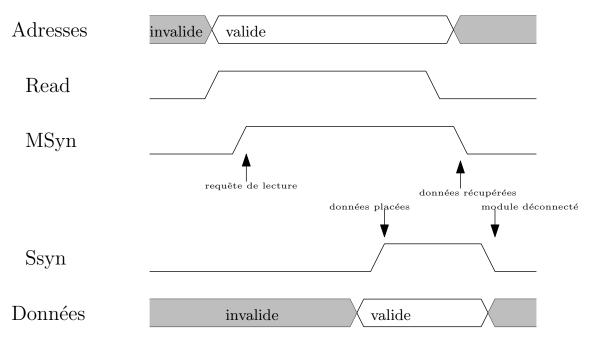

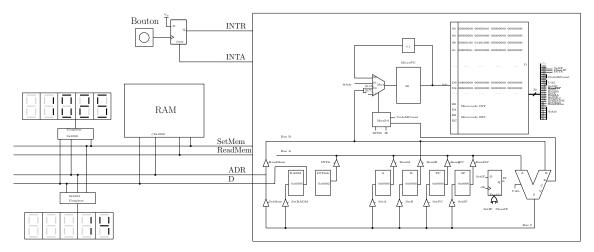

|              | 7.1            | Les périphériques d'entée/sortie                                     | 103 |

|              |                | 7.1.1 Quelques exemples de périphériques                             | 103 |

|              |                | 7.1.2 Connexions entre le processeur et les périphériques            | 104 |

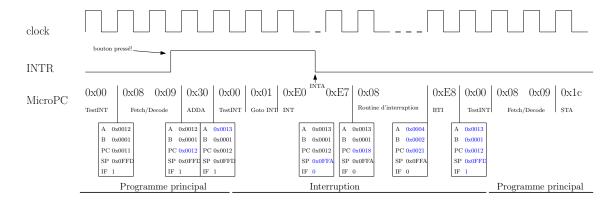

|              | 7.2            | Évènements synchrones et asynchrones : Déroutements et interruptions | 107 |

|              |                | 7.2.1 Les déroutements                                               | 107 |

|              |                | 7.2.2 Les interruptions                                              | 108 |

|              | 7.3            | Examples d'utilisation des interruptions                             | 111 |

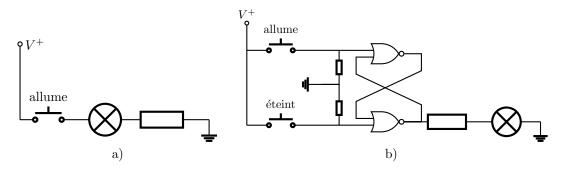

|              |                | 7.3.1 Un programme principal et un bouton                            | 111 |

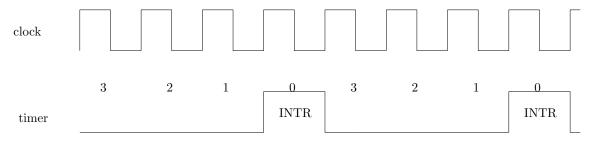

|              |                | 7.3.2 Timesharing et ordonnanceur pré-emptif                         | 113 |

|              | 7.4            | Gérer plusieurs interruptions                                        | 115 |

|              |                |                                                                      |     |

| $\mathbf{A}$ | Car            | te de référence                                                      | 119 |

**123**

## Chapitre 1

# Codages et opérations binaires

#### 1.1 Représentation des entiers naturels

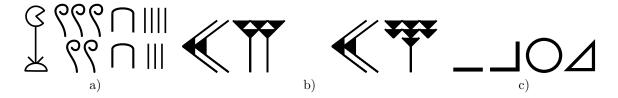

On va ici s'intéresser à la représentation d'un entier naturel. Quand on parle de représentation, il faut bien distinguer le représentant du représenté, et cette distinction est valable quel que soit le langage utilisé et quel que soit l'objet à représenter. Sur la figure 1.1, vous trouverez différents symboles pour représenter des nombres, utilisés par les Egyptiens, les Mésopotamiens et les Shadoks.

FIGURE 1.1 – a) Les egyptiens utilisaient un système additif. Chaque symbole représente une puissance de 10 et est répété autant de fois que nécessaire avec, en partant de la droite : les unités, les dizaines, les centaines et les milliers. Ici, nous avons la représentation de 1527. b) Les Mésopotamiens utilisaient un système mixte additif et positionnel en base 60 il y a environ 4000 ans. Chaque nombre entre 1 et 59 (le zéro allait bientôt apparaître) possède un symbole (en fait, les nombres 1, .. 9 puis 10, 20, .. 50 possède chacun leur symbole, les autres nombres 11, 12, ...49, 51, 52 .. sont construits à partir des premiers) et c'est sa position qui détermine la puissance de 60 à lui affecter. Ici, nous avons la représentation de  $1527 = (20 + 5) * 60^1 + (20 + 7) * 60^0$ . Source : https://fr.wikipedia.org/. c) Le nombre Bu-Zo-Ga-Mu dans le système de numération Shadok, en base 4, soit le nombre  $99 = 1.4^3 + 2.4^2 + 0.4 + 3$ .

Les Egyptiens par exemple représentaient les nombres en base 10 avec un système additif : un symbole est affecté à chaque puissance de 10 et le nombre représenté est égal à la somme des valeurs des symboles. Comme chaque puissance de dix possède un unique symbole la représentant, la position des symboles n'influence pas la valeur représentée. Les Mésopotamiens utilisaient un système mixte positionnel et additif : un symbole est affecté aux unités et aux dizaines entre 1 et 59, ces symboles sont regroupés par paquet dont la valeur est égale à la somme des valeurs des symboles et chaque groupe de symboles se voit affecté une puissance de 60 croissante de droite à gauche. Sur la figure 1.1b, il y a deux paquets de symbole; le paquet le plus à droite code 20 + 7, et le paquet le plus à gauche 20 + 5. La valeur représentée est donc décodée en affectant la puissance  $60^{\circ}$  à 27 et  $60^{\circ}$  à 25 ce qui nous donne : 60 \* 25 + 27 = 1527. On utilise encore de nos jours différentes bases pour représenter des nombres : la base 10 mais aussi les bases 24 et 60 pour les heures, minutes et secondes ou les angles en degrés et comme on va le voir, les bases 2, 8 et 16 sont très utilisées en informatique. Avant de se focaliser exclusivement sur les représentations en base 2 et 16, je vous propose un petit détour assez général par les représentations positionelles en base p qui va nous permettre d'introduire quelques notions qu'on spécialisera ensuite sur les bases

qui nous intéressent.

#### 1.1.1 Représentation en base p

On s'intéresse maintenant uniquement aux systèmes positionnel. Dans un système positionnel en base  $p \in \mathbb{N}$ ,  $p \geq 2$ , un entier naturel n s'écrit de manière unique sous la forme $(a_{k-1}a_{k-2}\cdots a_1a_0)_p$  avec  $\forall i, a_i \in [0, p-1], a_{k-1} \neq 0$ . La valeur associée à cette représentation est donnée par :

$$n = \sum_{i=0}^{k-1} a_i p^i$$

Par exemple, en base 10 la représentation 34 a pour valeur 34  $(a_1 = 3, a_0 = 4)$  puisque :

$$34 = 3.10^1 + 4.10^0$$

On a l'habitude de travailler en base 10 et on ne précise donc jamais la base dans laquelle on travaille mais il faut faire attention au fait que la valeur d'une représentation dépends de sa base. Par exemple si 34 est interprété en base 16, sa valeur vaut  $3.16^1 + 4.16^0 = 52$ . C'est pour cette raison qu'on précisera la base p d'une représentation en notant  $34_{10}$  pour la représentation de 34 en base 10, ou  $34_{16}$  pour la représentation de 52 en base 16. Quand la base n'est pas spécifiée, c'est qu'on considère la représentation en base 10.

Posons nous maintenant la question du changement de la base d'une représentation. Nous savons déjà passer de la représentation en base p à la représentation en base 10:

$$n = \sum_{i=0}^{k-1} a_i p^i$$

Étant donnée la représentation en base 10 d'un entier naturel n, sa représentation en base p s'obtient quand à elle en appliquant des divisions Euclidiennes successives par p. En effet, il suffit de noter que :

$$n = \sum_{i=0}^{k-1} a_i p^i = a_0 + p.(\sum_{i=0}^{k-2} a_{i+1} p^{i+1})$$

Le reste de la division Euclidienne de n par p est donc  $a_0$ , le premier chiffre de la représentation de n en base p. En répétant l'opération sur le quotient, on obtient tout les chiffres de la représentation de n en base p. Par exemple :

Je n'ai pas utilisé, dans l'exemple précédent, les symboles mésopotamiens dans la représentation en base 60, et j'ai plutôt regroupé les chiffres de la représentation par des < . >.

#### 1.1.2 Représentation binaire, p=2

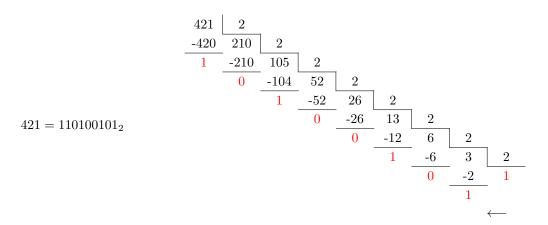

Lorsque la base p=2, on parle de représentation binaire. On utilise alors uniquement les chiffres ou bits 0 et 1. Par exemple, la représentation binaire du nombre n=421 est :

Pour retrouver la valeur représentée, il suffit d'appliquer la formule  $\sum_i a_i p^i$ . Comme, en binaire,  $a_i \in \{0,1\}$ , cela revient à sommer les puissances de deux pour lesquelles  $a_i = 1$ :

Et on a bien 421 = 256 + 128 + 32 + 4 + 1. La représentation binaire est parfois notée avec le préfixe 0b. On notera alors : 421 = 0b110100101. Une représentation binaire sur k bits peut représenter les entiers dans  $[0, 2^k - 1]$ . Par exemple, sur 32 bits, on peut représenter la plage d'entiers [0, 4.294.967.295]. Dans la représentation binaire  $a_{k-1} \cdots a_0$ , le premier bit  $a_{k-1}$  est appelé **bit de poids fort** et le dernier bit  $a_0$  est appelé **bit de poids faible**. Un regroupement de 8 bits est appelé un octet (byte en anglais). Un mot de 32 bits contient donc 4 octets. Un octet (10) peut représenter des entiers naturels dans le domaine [0, 255]. On utilise couramment en informatique des multiples de l'octet : le kilooctet ( $10 = 10240 = 2^{10}$ ), le megaoctet (10 = 10240 = 10240), le gigaoctet (10 = 10240) et de plus en plus fréquemment le téraoctet (10 = 10240). Par exemple, les disques durs grand public atteignent facilement en 2015 une capacité de quelques téraoctets.

#### 1.1.3 Représentation hexadécimale, p=16

Lorsque la base p=16, on parle de représentation hexa décimale. Pour n'utiliser qu'un seul symbole par chiffre, on utilise par convention un mélange de chiffres et de lettres  $0,1,\cdots,9,A,B,\cdots,F$  pour représenter les valeurs  $0,1,\ldots 9,10,\ldots 15$ . Par exemple, la représentation hexa décimale de 421 est :

La représentation hexadécimale est parfois notée avec le préfixe  $0\times$ . On notera alors  $421=0\times1A5$ .

#### 1.1.4 Raccourcis de conversion binaire/hexadécimal

Comme la base hexadécimale est multiple de la base binaire  $16 = 2^4$ , on peut très facilement passer d'une représentation binaire à une représentation hexadécimale et vice versa. Il suffit pour cela de grouper les bits par paquets de 4:

$$421_{10} = (\overbrace{0001}^{(1)} \quad \overbrace{1010}^{A} \quad \overbrace{0101}^{5)_{16}})_{2}$$

Pour la conversion hexadécimale vers binaire, il suffit de mettre bout à bout les représentations binaires de chacun des chiffres de la représentation hexadécimale.

#### 1.1.5 Codage Binary Coded Décimal et Codage de Gray

On verra un peu plus tard que pour certaines utilisations, d'autres codage que ceux présentés jusque maintenant sont très pratiques. Le codage BCD "Binary Coded Decimal" est, disons, un système à deux niveaux. Pour construire la représentation BCD du nombre 421, on met simplement bout à bout les représentations binaires sur 4 bits <sup>1</sup> de chacun des chiffres 4, 2, 1 (d'où le nom décimal codé binaire) :

$$421 = \overbrace{010000100001}^{4} \underbrace{0001}^{2}$$

On verra un peu plus tard que ce codage est particulièrement adapté lorsqu'on souhaite afficher des nombres. Dans une représentation binaire naturelle disons, les chiffres des unités, dizaines, etc.. sont complètement mélangés. Si on veut afficher un entier (sur un afficheur 7 ségments, comme on le verra en TP), il est nécessaire de dissocier les représentations de chacun des chiffres, ce que permet le codage BCD.

Le codage de Gray a été introduit dans les années 1950. Contrairement au codage binaire introduit précédemment, il n'y qu'un et un seul bit qui change entre la représentation des valeurs n et n+1. Vous trouverez ci-dessous une comparaison entre un codage binaire comme introduit précédemment et le code de Gray.

| valeur | représentation binaire | représentation de Gray |

|--------|------------------------|------------------------|

| 0      | 000                    | 000                    |

| 1      | 001                    | 001                    |

| 2      | 010                    | 011                    |

| 3      | 011                    | 010                    |

| 4      | 100                    | 110                    |

| 5      | 101                    | 111                    |

| 6      | 110                    | 101                    |

| 7      | 111                    | 100                    |

Il a été introduit notamment pour éviter des états transitoires indésirables lorsqu'on incrémente un nombre <sup>2</sup> et s'avère également très pratique lorsqu'on est amené à simplifier des expressions booléennes avec des tableaux de Karnaugh.

# 1.2 Opérations arithmétiques sur les représentations non signées

L'addition de nombres représentés en base p se fait comme on a l'habitude en base 10. On commence par additionner les chiffres "les plus à droite" et on propage l'éventuelle retenue. Par exemple, en binaire, l'addition  $4_{10} = 1_{10} + 3_{10} = 001_2 + 011_2 = 100_2$  s'écrit <sup>3</sup>:

<sup>1.</sup> Il faut 4 bits pour représenter tous les chiffres de 0 à 9

<sup>2.</sup> Avec une représentation binaire, si un circuit incrémenteur n'a pas la même lattence pour modifier les valeurs des bits, on pourrait, en allant de  $001_2=1$  à  $010_2=2$ , passer par la représentation  $011_2=3$ , ce qui n'est pas le cas avec le codage de Gray puisqu'un seul bit change à chaque étape

<sup>3.</sup> En toute rigueur, nous devrions utiliser un symbole différent pour représenter l'addition entre les représentations dans différentes bases puisque ces opérations travaillent sur des éléments provenant d'ensembles différents

Comme il y a unicité des représentations en base p, vous pouvez aussi tout à fait passer par la base 10 pour faire vos calculs et retourner ensuite en base  $p \ge 2$ :

$$(p-1)_p + (p-1)_p = (p-1)_{10} + (p-1)_{10} = p_{10} + (p-2)_{10} = (1 < p-2)_p$$

Concentrons nous maintenant sur la base p=2 puisque je ne vous cache pas que nous allons essentiellement nous intéresser aux opérations arithmétiques binaires. Commençons par construire la table d'addition de deux bits en dissociant le reste de la retenue (Table 1.1) :

|   |   |         |       | a | b | r | Retenue | Reste |

|---|---|---------|-------|---|---|---|---------|-------|

|   |   |         |       | 0 | 0 | 0 | 0       | 0     |

| a | b | Retenue | Reste | 0 | 1 | 0 | 0       | 1     |

| 0 | 0 | 0       | 0     | 1 | 0 | 0 | 0       | 1     |

| 0 | 1 | 0       | 1     | 1 | 1 | 0 | 1       | 0     |

| 1 | 0 | 0       | 1     | 0 | 0 | 1 | 0       | 1     |

| 1 | 1 | 1       | 0     | 0 | 1 | 1 | 1       | 0     |

|   |   | ļ       |       | 1 | 0 | 1 | 1       | 0     |

|   |   |         |       | 1 | 1 | 1 | 1       | 1     |

TABLE 1.1 — Tables d'addition de deux bits avec éventuellement une retenue. Chacun des résultats peut se diviser en une retenue et un reste. Par exemple  $1_2 + 1_2 + 1_2$  produit le reste  $1_2$  et la retenue  $1_2$ .

Les résultats de ce tableau d'addition peuvent être divisés en deux parties : la retenue et le reste. Par exemple,  $0_2+0_2$  produit la retenue  $0_2$  et le reste  $0_2$  alors que  $1_2+1_2$  produit la retenue  $1_2$  et le reste  $0_2$ . D'ailleurs, de manière générale, notez qu'en base  $p \geq 2$ , la retenue sera toujours 0 ou 1 puisque  $(p-1)_p+(p-1)_p=(1< p-2>)_p$  et  $(p-1)_p+(p-1)_p+1_p=(1< p-1>)_p$ ; ce qui donne par exemple : 9+9=18,9+9+1=19;  $F_{16}+F_{16}=1E_{16}$ ;  $F_{16}+F_{16}+1=1F_{16}$ ;  $1_2+1_2=10_2$  et  $1_2+1_2+1_2=11_2$ .

Nous pouvons maintenant introduire un algorithme calculant l'addition de deux entiers naturels et travaillant directement sur les représentations binaires de ces entiers. L'algorithme 1 n'est rien d'autre que l'addition telle qu'on l'a apprise à l'école, c'est à dire posée.

#### Algorithme 1 Addition de deux entiers naturels représentés en binaire

```

1: function Addition (a, b)

2: r \leftarrow 0

3: for i = 0 à n - 1 do

4: c_i = \text{reste}(a_i + b_i + r)

5: r = \text{retenue}(a_i + b_i + r)

6: c_n = r

7: return (c_n c_{n-1} ... c_0)

```

En sommant deux représentations sur n bits, on peut avoir besoin de n+1 bits pour représenter le résultat tel que le bit de poids fort soit non nul. Par exemple  $11_2+01_2=100_2$ . Dans ce cas, on dira que le résultat est le résultat sur n bits, le n+1 ième bit étant appelé la retenue (carry). Par exemple le résultat sur 2 bits de  $11_2+01_2$  est  $00_2$  avec une retenue r=1.

L'algorithme d'addition 1 est naı̈f et nécessite de répéter n fois les opérations "retenue" et "reste". Des algorithmes plus performants, comme l'algorithme de Kogge-Stone permettent de réaliser cette opération en un nombre d'étapes de l'ordre de  $K \times \log(n)$  avec K une certaine constante indépendante de n.

La soustraction peut se poser de la même façon, mais cette fois-ci avec l'emprunt de la retenue si besoin. Je vous représente ci-dessous les différentes étapes pour calculer la soustraction binaire  $100_2 - 001_2$ :

Dans la soustraction,  $100_2 - 001_2$ , la première opération  $0_2 - 1_2$  nécessite d'emprunter une retenue qui est propagée jusqu'au premier chiffre non nul (jusqu'aux "centaines"). L'emprunt d'une retenue aux "centaines" annule le chiffre des "centaines", fait apparaître un deux aux "dizaines" (puisque  $2^3 = 2.2^2$ ) auquel on emprunte également une retenue. On finit par faire la soustraction 2 - 1 = 1. On fait exactement la même chose en base 10, lorsqu'une centaine vaut 10 dizaines et qu'une dizaine vaut 10 unités :

Comment faire quand la première opérande est plus petite que la deuxième? Nous allons le voir dans un instant en introduisant des représentations pour les entiers relatifs, dont une particulièrement adaptée pour faire des opérations de soustraction sur les entiers.

La multiplication en base p se fait, comme on a appris à l'école, en la posant. En binaire, la multiplication est encore plus simple puisqu'elle repose uniquement sur des décalages et des additions. En effet  $11_2 \times 1_2 = 11$ ,  $11_2 \times 10_2 = 110$ , ..; Ainsi :  $11_2 \times 11_2 = 11_2 \times 1_2 + 11_2 \times 10_2 = 11_2 + 110_2 = 1001_2$  (on retrouve bien  $3 \times 3 = 9$ ). Pour la division, on peut aussi procéder en posant la division en base 2 comme on a appris à la poser en base 10.

# 1.3 Représentations et opérations avec un nombre fixé de bits

Jusqu'à maintenant, on ne s'est pas trop soucié du nombre de bits à utiliser pour construire des représentations. Après tout,  $10_2 = 2$ ,  $100_2 = 4$ , 1000 = 8, ... et on pourrait se dire qu'il suffit d'utiliser un nombre de bits suffisant pour représenter une valeur. Sauf que pour réaliser physiquement un ordinateur, il faut se fixer le nombre de bits qu'on va utiliser. Par exemple, les ordinateurs dits "32 bits" et "64 bits" utilisent respectivement des représentations des entiers sur 32 et 64 bits. Se fixant un nombre de bits n, on ne peut pas représenter plus de  $2^n$  valeurs différentes. Le plus petit entier naturel représentable est 0 et le plus grand entier représentable est  $\sum_{i=0}^{n-1} 2^i = 2^n - 1$ . Par exemple, sur une machine 32 bits, les entiers naturels sont limités à la plage [0, 4.294.967.295].

#### 1.4 Représentation des entiers relatifs

Le problème de la représentation des entiers négatifs a connu plusieurs réponses au début du développement des ordinateurs. Nous allons notamment voir deux représentations simples (la représentation par offset et la représentation par valeur signée) mais qui ont chacune un inconvénient avant d'introduire la représentation par complément qui s'est imposée. Le problème de la représentation des nombres négatifs consiste à trouver une représentation des entiers relatifs sur n bits qui permettent de réaliser facilement le codage/décodage en base 10 et les opérations arithmétiques.

#### Codage par offset

Le codage par offset (excess-K,  $offset\ binary$ ) est la façon la plus simple de représenter des k bits

entiers négatifs et positifs. Il consiste à représenter l'entier le plus négatif par  $000\cdots 0$  et l'entier le k bits

plus positif par  $111 \cdots 1$ . Par convention, on représente la plage des entiers  $[-2^{k-1}, 2^{k-1} - 1]$  (qui contient  $2^k$  valeurs). Par exemple, la table ci-dessous donne le codage des entiers par offset pour k=3 bits :

Pour coder un entier relatif  $n \in [-2^{k-1}, 2^{k-1} - 1]$ , on commence par lui ajouter  $K = 2^{k-1}$  et on calcule la représentation non signée de l'entier positif  $n + 2^{k-1}$ . C'est le fait d'ajouter cette constante  $K = 2^{k-1}$  qui donne le nom de codage par offset. Remarquez qu'on pourrait choisir une valeur d'offset différente de  $2^{k-1}$  pour déplacer arbitrairement, selon les besoins, la plage des entiers représentés. Pour décoder la valeur en base 10 d'un nombre codé par offset  $a_{k-1}a_{k-2}\cdots a_1a_0$ , il suffit de décoder la valeur comme si nous représentions un entier non signé et de soustraire au résultat l'offset K, en d'autres termes :

$$n = \sum_{i=0}^{k-1} a_i 2^i - 2^{k-1}$$

En codage par offset, l'entier n=0 est toujours représenté par un 1 sur le bit de poids fort et des k-1 bits

zéros sinon : 0 = 1  $0 \cdots 0$  . On remarquera que les entiers strictement négatif ont un bit de poids fort nul alors que les entiers positifs ont un bit de poids fort égal à 1.

L'addition avec des représentations par offset nécessite un circuit différent de l'addition des représentations non signées. En effet, si nous posons l'addition comme nous l'avons fait avec les représentations non signées, on obtient  $(-1)_{2K} + (1)_{2K} = (-4)_{2K}$ :

$$\begin{array}{cccccc} & 0 & 1 & 0 & 011_{2K} = -2 \\ + & 1 & 0 & 1 & 101_{2K} = 1 \\ \hline & 1 & 1 & 1 & 111_{2K} = 3 \end{array}$$

La représentation par offset n'a pas que des inconvénients. Elle a au moins un avantage, les opérations de comparaison sont très simples. Pour savoir si un nombre est plus grand qu'un autre, il suffit de comparer les représentations bit à bit de gauche à droite, c'est à dire le même circuit que pour comparer des représentations non signées <sup>4</sup>. Dés que deux bits diffèrent, on peut dire quel nombre est plus grand que l'autre :

#### Algorithme 2 Comparaison de deux représentations codées par offset

```

1: function Comparaison(a, b)

2:

i \leftarrow n-1

while a_i == b_i et i \geq 0 do

3:

i \leftarrow i - 1

4:

if i < 0 then

5:

return a égal à b

6:

else if a_i = 1 then

7:

\mathbf{return} \ a \ \mathbf{plus} \ \mathbf{grand} \ \mathbf{que} \ b

8:

9:

else

return a plus petit que b

10:

```

<sup>4.</sup> Un peu plus tard, nous introduisons le codage par complément à deux qui nécessite un circuit différent pour comparer les représentations non signées d'une part et les représentations signées d'autre part

#### Codage par valeur signée

Le codage par valeur signée (sign-magnitude) consiste à réserver le bit de poids fort pour coder le signe ( $a_{k-1}=0$  pour les entiers positifs et  $a_{k-1}=1$  pour les entiers négatifs) et le reste de la représentation  $a_{k-2}\cdots a_0$  pour représenter la valeur absolue de l'entier en représentation non

$$k-1$$

bits  $k-1$  bits

signée. L'entier n=0 admet alors deux codages 0  $0 \cdots 0$  (0 positif) ou 1  $0 \cdots 0$  (0 négatif). Il reste donc un nombre pair de nombres en excluant 0 et un codage sur k bits code donc la plage  $[-2^{k-1}+1,2^{k-1}-1]$ . Par exemple, la table ci-dessous donne la codage des entiers par valeur signée pour k=3 bits :

| Entier $n$               | -3         | -3   -2    |            | 0                        | 1          | 2          | 3          |

|--------------------------|------------|------------|------------|--------------------------|------------|------------|------------|

| Codage par valeur signée | $111_{2s}$ | $110_{2s}$ | $101_{2s}$ | $100_{2s}$ ou $000_{2s}$ | $001_{2s}$ | $010_{2s}$ | $011_{2s}$ |

Cette représentation a le désavantage d'avoir deux représentations pour le 0; Lorsqu'on doit vérifier si un résultat est nul, il faut se comparer à deux représentations possibles. Plus gênant, les opérations arithmétiques nécessitent des circuits différents des opérations arithmétiques sur les représentations non signées. En effet, si on utilise l'addition sur les représentations non signées, le résultat de 1 + (-1) est incorrect :

$$1 + (-1) = (001)_{2s} + (101)_{2s} = (110)_{2s} = -2$$

#### 1.4.1 Complément réduit et complément vrai

Les deux représentations introduites précédemment (par offset et par valeur signée) ont chacune l'inconvénient de nécessiter des circuits spécialisés (différents de ceux impliqués pour les opérations sur les représentations non signées) pour les opérations arithmétiques. Posons nous donc la question de la représentation des entiers négatifs de la manière suivante : soit une représentation  $a_{k-1}...a_0$  d'un entier a, quelle doit être la représentation  $b_{k-1}...b_0$  de la valeur -a de telle sorte que l'addition

posée donne

$$\overbrace{0000}^{k \text{ bits}}$$

?

Si on prends  $b_i = 1 - a_i$  et qu'on ajoute 1 au résultat , alors :

|     | $a_{k-1}$     | $a_{k-2}$     | • • • | $a_0$     |

|-----|---------------|---------------|-------|-----------|

| +   | $1 - a_{k-1}$ | $1 - a_{k-2}$ | • • • | $1 - a_0$ |

|     | 1             | 1             | 1     | 1         |

| +   | 0             | 0             | 0     | 1         |

| (1) | 0             | 0             | 0     | 0         |

On appelle **complément à un** de la représentation  $a_{k-1}...a_0$ , la représentation  $(1-a_{k-1})..(1-a_0)$ . Le codage par complément à un sur k bits d'un nombre négatif s'obtient en inversant tout les bits (remplacer les 0 par des 1 et les 1 par des 0) de la représentation non signée de sa valeur absolue sur k-1 bits. Par exemple, avec k=3 bits :

$$3 = 011_2; -3 = 100_2$$

On appelle **complément à deux** de la représentation  $a_{k-1}...a_0$ , la représentation  $(1-a_{k-1})..(1-a_0)+1$ . Le codage par complément à deux s'obtient simplement en inversant tout les bits (pour construire le complément à un) et à ajouter 1 au résultat. La table ci-dessous donne le codage des entiers par complément pour k=3 bits :

| Entier $n$                   | -4  | -3  | -2  | -1  | 0          | 1   | 2   | 3   |

|------------------------------|-----|-----|-----|-----|------------|-----|-----|-----|

| Codage par complément à un   | -   | 100 | 101 | 110 | 111 ou 000 | 001 | 010 | 011 |

| Codage par complément à deux | 100 | 101 | 110 | 111 | 000        | 001 | 010 | 011 |

Notez que pour la représentation de "0", on part de "000", on calcule son complément à 1, soit "111" auquel on ajoute 1 en gardant le résultat sur 3 bits et donc en ignorant la retenue. Quelques exemples supplémentaires :

$$42 = 0010$$

$1010$  complément à un  $1101$   $0101 \stackrel{+1}{\Rightarrow} 1101$   $0110 = -42$   $-42 = 1101$   $0110$  complément à un  $0010$   $1001 \stackrel{+1}{\Rightarrow} 0010$   $1010 = 42$

Le "complément à un" donne deux représentations du 0 et permet de représenter la plage des entiers  $[-2^{k-1} + 1, 2^{k-1} - 1]$ . La représentation par complément à deux ne donne qu'une représentation du 0 et permet de représenter les entiers  $[-2^{k-1}, 2^{k-1} - 1]$ . Le bit de poids fort d'un nombre négatif est à 1, le bit de poids fort d'un nombre positif est à 0.

On retiendra les étapes de conversion suivante. Pour convertir un entier  $n \in [-2^{k-1}, 2^{k-1} - 1]$  dans sa représentation en complément à deux :

- Si  $n \geq 0$ , on calcule sa représentation non signée

- Si n < 0, on calcule la représentation non signée de -n, on inverse tout les bits et on ajoute 1

Pour calculer la valeur décimale d'une représentation par complément  $a_{k-1}...a_0$ :

- si  $a_{k-1} = 0$ , le nombre est positif et sa valeur est  $\sum_{i=0}^{k-2} a_i 2^i$ ,

- si  $a_{k-1} = 1$ , le nombre est négatif. Sa valeur absolue est calculée en complémentant la représentation  $(1 a_{k-2})..(1 a_0) + 1$  et en calculant sa valeur.

On peut aussi directement calculer la valeur décimale d'une représentation par complément à deux grâce à la formule :  $(a_{k-1}...a_0)_2 = -a_{k-1}2^{k-1} + \sum_{i=0}^{k-2} a_i 2^i$ .

#### 1.5 Opérations arithmétiques sur les représentations signées

#### 1.5.1 Additions/Soustractions

Nous considérons ici uniquement la représentation par complément à deux, car, comme nous l'avons esquissé précédemment, cette représentation facilite les opérations arithmétiques. L'addition en complément à deux se réalise de la même façon que l'addition sur les représentations non signées :

| a | b | r | Retenue | Reste |

|---|---|---|---------|-------|

| 0 | 0 | 0 | 0       | 0     |

| 0 | 1 | 0 | 0       | 1     |

| 1 | 0 | 0 | 0       | 1     |

| 1 | 1 | 0 | 1       | 0     |

| 0 | 0 | 1 | 0       | 1     |

| 0 | 1 | 1 | 1       | 0     |

| 1 | 0 | 1 | 1       | 0     |

| 1 | 1 | 1 | 1       | 1     |

#### Algorithme 3 Addition de deux entiers relatifs représentés en complément à deux

```

1: function Addition(a, b)

Require: Deux entiers a = (a_{n-1}...a_0)_2, b = (b_{n-1}...b_0)_2 codés sur n bits

Ensure: La représentation (c_{n-1}...c_0)_2 sur n bits de c = a + b

2: r \leftarrow 0

3: for i = 0 à n - 1 do

4: c_i \leftarrow \text{reste}(a_i + b_i + r)

5: r \leftarrow \text{retenue}(a_i + b_i + r)

6: return (c_n c_{n-1}..c_0)

```

Par exemple, pour réaliser l'opération 3 + (-2) sur k = 3 bits, on commencera par construire les représentations par complément à deux de 3 et -2:

```

3 = (011)_2

```

$$2 = (010)_2 \Rightarrow (-2) = (110)_2$$

et on posera l'addition :

$$0 \quad 1 \quad 1 \\ + \quad 1 \quad 1 \quad 0 \\ \hline (1) \quad 0 \quad 0 \quad 1$$

La valeur décimale de la représentation en complément à deux 001 est :  $-0 \times 2^3 + 1 = 1$ . Calculons maintenant 2 + (-3) :

$$3 = (011)_2 \Rightarrow (-3) = (101)_2$$

$2 = (010)_2$

et on pose l'addition :

$1 \quad 0 \quad 1$

$+ \quad 0 \quad 1 \quad 0$

La valeur décimale de la représentation en complément à deux 111 est :  $-1 \times 2^3 + 1 + 2 + 4 = -1$ . On trouve également la valeur décimale en complémentant  $\overline{111_2} + 001_2 = 001_2 = 1$  et en retournant l'opposé.

Utilisant un nombre fixé de bits pour représenter les valeurs, certaines opérations peuvent conduire à des résultats faux. Lorsque le résultat d'une opération arithmétique est plus petit que le plus entier représentable ou plus grand que le plus grand entier représentable, on peut avoir un dépassement de capacité (**overflow**). Le dépassement de capacité apparaît lorsque l'addition de deux nombres positifs conduit à la représentation d'un nombre négatif ou lorsque l'addition de deux nombres négatifs conduit à la représentation d'un nombre positif; il ne peut jamais apparaître lors de l'addition d'un nombre positif et d'un nombre négatif. Par exemple, si on additionne 3+3 sur k=3 bits, un dépassement de capacité se produit :

En effet  $110_2$  est la représentation en complément à deux du nombre négatif  $-6 \neq 3+3$ . Le problème apparaît aussi en additionnant des nombres négatifs, (-3) + (-3) sur k=3 bits. Les représentations en complément à deux de -3 étant  $101_2$ , l'addition donne :

La représentation  $010_2$  a pour valeur  $2 \neq -6$  en complément à deux. Dans le cas précédent, il y a overflow et génération d'une retenue mais il n'y a pas équivalence entre les deux. L'exemple cidessous conduit à la génération d'une retenue sans pour autant qu'il y ait dépassement de capacité.

Une règle que je ne détaillerais pas est qu'il y a dépassement de capacité si et seulement si la retenue entrante lors du calcul du bit le plus à gauche (le bit de signe) est différente de la retenue sortante. Nous ne détaillerons pas plus le débordement de capacité mais c'est un aspect à prendre en compte lorsqu'on réalise des circuits réalisant ces opérations arithmétiques.

# 1.6 Représentation des nombres réels : virgule fixe et virgule flottante

#### 1.6.1 Représentation par virgule fixe (fixed-point)

On va maintenant rapidement présenter des représentations de nombres réels en introduisant la représentation à virgule fixe et la représentation à virgule flottante. Pour comprendre la représentation par virgule fixe, commençons par regarder un exemple en décimal. Le nombre décimal 26.5 peut se décomposer, en étendant ce que nous avons fait lorsque nous avons introduit la représentations des entiers naturels, de la manière suivante :

$$26.5 = 2 \times 10^{1} + 6 \times 10^{0} + 5 \times 10^{-1}$$

Si on utilise maintenant une représentation binaire, on peut affecter à chacune des positions une puissance de  $2:2^2,2^1,2^0,2^{-1},2^{-2},...$  Le seul problème est de savoir où placer la virgule lorsqu'on voit la représentation 110101. Si la virgule se trouve à la fin du mot, alors  $110101_2 = 2^0 + 2^2 + 2^4 + 2^5 = 53$ . Si la virgule se trouve juste avant la fin du mot, disons 11010.1, alors :  $11010.1 = 2^{-1} + 2^1 + 2^3 + 2^4 = 26.5$ . Il n'y a pas d'autre choix que de se fixer une convention en précisant le nombre de bits  $n_e$  utilisés pour représenter la partie entière et le nombre de bits  $n_f$  utilisés pour représenter la partie fractionaire. Une représentation à virgule fixe avec  $n_e$  bits pour la partie entière et  $n_f$  bits pour la partie fractionaire sera notée  $Q < n_e > . < n_f >$ . Par exemple, Q2.14 utilise 2 bit pour la partie entière et 14 bits pour la partie fractionnaire avec une représentation sur 16 bits en tout.

Pour construire la représentation à virgule fixe du nombre réel 26.5, on isolera la partie entière 26 et la partie fractionnaire .5 La partie entière s'écrit  $26 = 16 + 8 + 2 = (11010)_2$  et la partie fractionnaire  $0.5 = 2^{-1}$ . Avec une représentation à virgule fixe Q7.1, le réel 26.5 s'écrit 00110101. On peut remarquer que certaines opérations s'effectuent très simplement avec une représentation par virgule fixe. Par exemple, multiplier par 2 la représentation 00110101 revient à décaler la représentation à gauche et à construire sur 8 bits la représentation 01101010 dont la valeur  $^5$ , dans une représentation Q7.1 est :

$$\sum_{i=0}^{k-1} a_i 2^{i-n_f} = 0 \times 2^{-1} + 1 \times 2^0 + 0 \times 2^1 + 1 \times 2^2 + 0 \times 2^3 + 1 \times 2^4 + 1 \times 2^5 + 0 \times 2^6$$

$$= 1 + 4 + 16 + 32 = 53$$

Remarquez que pour calculer la valeur décimale d'une représentation  $Q < n_e > < n_f >$ , il suffit d'interpréter la représentation comme une représentation d'un entier naturel et de multiplier la valeur décimale trouvée par  $2^{-n_f}$  puisque :

$$\sum_{i=0}^{k-1} a_i 2^{i-n_f} = 2^{-n_f} \sum_{i=0}^{k-1} a_i 2^i$$

Et on retrouve à droite de l'équation le terme  $\sum_{i=0}^{k-1} a_i 2^i$  pour calculer la valeur décimale d'un **entier naturel**.

Comme pour la représentation des entiers négatifs utilisait le complément à deux, la représentation des nombres négatifs en virgule fixe utilise également le complément à deux. Par exemple, en notation à virgule fixe Q4.2, le réel 3.5 s'écrit :  $3.5 = 2^1 + 2^0 + 2^{-1} = 001110_2$ . Son complément à deux est  $-3.5 = 110010_2$ . On peut alors calculer 5.25 - 3.5:

Comme le bit de poids fort de  $111\underline{001}_2$  est égal à un, le nombre est négatif, son opposé est représenté par le complément à deux de  $\overline{111001}_2+1_2=000111_2$  dont la valeur avec la représentation Q4.2 est bien  $1\times 2^0+1\times 2^{-1}+1\times 2^{-2}=1.75$ . Pour calculer directement la valeur décimale a d'une représentation signée à virgule fixe  $a_{k-1}...a_0$  dans un système  $Q< n_e>< n_f>$ , il faut utiliser une formule similaire au calcul de la valeur d'un entier d'une représentation en complément à deux :

$$a_{10} = 2^{-n_f} (-a_{k-1}2^{k-1} + \sum_{i=0}^{k-2} a_i 2^i), k = n_e + n_f$$

La valeur signée de  $111001_2$  est -7, donc la valeur de  $111001_2$  dans le système Q4.2 est  $2^{-2} \times (-7) = -1.75$ .

<sup>5.</sup> la formule pour calculer la valeur s'applique ici parce que la valeur en positive. Si des nombres négatifs sont représentés, comme décrit un peu plus loin, il faudra faire attention au bit de signe

Pour finir, remarquez que les opérations arithmétiques sur les représentations à virgule fixe sont identiques aux opérations arithmétiques sur les entiers, contrairement aux opérations arithmétiques sur les représentations à virgule flottante que nous allons voir dans un instant. Cela conduit parfois à préférer cette représentation dans des applications de traitement du signal.

#### 1.6.2 Représentation par virgule flottante (floating-point)

Dans les années 1980-1990, le standard IEEE-754 a été introduit pour représenter les nombres réels avec une représentation dite à virgule flottante. Une version mise à jour a été proposée en 2008 [IEE, 2008]. Le standard a été mis au point pour apporter un certain nombre de garanties quand aux erreurs introduites par le fait qu'on travaille en précision finie. Ce standard permet également de représenter l'ensemble étendu des réels auquel est ajouté des nombres spéciaux qNan et sNan :  $S = \mathbb{R} \cup \{-\infty, \infty\} \cup \{\text{sNan}, \text{qNan}\}$ . Les "nombres" sNan et qNan permettent de gérer des exceptions en représentant les résultats d'opérations telles que  $0/0, \infty/\infty, \sqrt{x}, x < 0, \ldots$ .

La représentation par virgule flottante est basée sur la notation scientifique des nombres. La notation scientifique d'un nombre décimal est de la forme :

En base

$$10: x = \pm m \times 10^e, m \in [0, 10[, e \in \mathbb{Z}$$

Dans cette notation, m est appelé la mantisse, et e l'exposant. Il existe des valeurs pour lesquelles plusieurs représentations sont possibles dans cette notation. Par exemple,  $1245 = 1.245 \times 10^3 =$  $0.1245 \times 10^4 = 0.01245 \times 10^5$ . Dans le standard IEEE, les représentations  $0.1245 \times 10^4$ ,  $0.01245 \times 10^5$ , ..., i.e. telles que  $m \in [0,1[$ , sont appelées les représentations dénormalisées de la valeur 1245. La représentation  $1.245 \times 10^3$ , i.e. telle que  $m \in [1, 10]$ , est appelée la représentation normalisée de la valeur 1245. La chose importante à noter ici est qu'il peut exister plusieurs représentations dénormalisées mais une unique représentation normalisée 6. Un nombre fixé de bits étant utilisé pour représenter la mantisse (m = 1.245, m = 0.1245,m = 0.01245), la représentation normalisée est celle qui utilise au mieux l'espace de représentation puisque les représentations dénormalisées occupent de l'espace inutilement pour représenter les 0 en tête du nombre. Néanmoins, ces représentations dénormalisées permettent d'accroître le domaine représentable puisque e est borné. Prenons un exemple, si l'exposant  $e \in [-128, 127]$  et supposons qu'on s'autorise 3 chiffres pour représenter la mantisse. Si nous considérons uniquement des représentations normalisées, le plus petit nombre positif non nul représentable est  $1.00 \times 10^{-128}$ . En autorisant des représentations dénormalisées, le plus petit nombre positif non nul représentable est  $0.01 \times 10^{-128}$ .

En généralisant à n'importe quelle base p, la notation scientifique s'écrit :

En base p:

$$x = \pm m \times p^e, m \in [0, p], e \in \mathbb{Z}$$

et en binaire, on a la propriété intéressante que la mantisse est toujours comprise dans l'intervalle [0, 2], i.e. le bit de poids fort de la mantisse est 0 ou 1 :

En base

$$2: x = \pm m \times 2^e, m \in [0, 2], e \in \mathbb{Z}$$

Pour représenter un nombre réel sous la forme d'une séquence de bits, il faut représenter :

- le signe : 1 bit suffit

- la mantisse sur  $n_m$  bits

- l'exposant sur  $n_e$  bits

pour un total de  $k = 1 + n_m + n_e$  bits. Le standard IEEE-754 introduit plusieurs standards binary - k en précisant la taille des mots pour représenter la mantisse et l'exposant, en voici quelques un :

- binary-16: k = 16 bits, 1 bit de signe,  $n_e = 5$  bits pour l'exposant,  $n_m = 10$  bits pour la mantisse

- binary-32 : k=32 bits, 1 bit de signe,  $n_e=8$  bits pour l'exposant,  $n_m=23$  bits pour la mantisse

- binary-64: k = 64 bits, 1 bit de signe,  $n_e = 11$  bits pour l'exposant,  $n_m = 52$  bits pour la mantisse

<sup>6.</sup> Cela veut notamment dire que pour comparer deux nombres en virgule flottante, il faudra s'assurer de normaliser les représentations et ne pas faire une comparaison bit à bit naïvement

Schématiquement, une représentation à virgule flottante se présente comme ci-dessous :

signe S (1 bit) | exposant E

$$(n_e \text{ bits})$$

| mantisse M  $(n_m \text{ bits})$

La valeur v de cette représentation s'obtient alors comme suit :

- Si

$$E = 11 \cdots 1_2 = 2^{n_e} - 1$$

et  $M = 00 \cdots 0_2 = 0$ , alors  $v = (-1)^S \infty$ ,

— Si

$$E = 11 \cdots 1_2 = 2^{n_e} - 1$$

et  $M \neq 0$ , alors  $v \in \{\text{qNan, sNan}\}$ ,

— Si

$$E = 00 \cdots 0_2 = 0$$

et  $M = 00 \cdots 0_2 = 0$ , alors  $v = (-1)^S 0$ , i.e.  $(\pm 0)$ ,

— Si

$$E=00\cdots 0_2=0$$

et  $M\neq 0$ , alors nous avons une représentation dénormalisée et

$$v = (-1)^S \cdot 2^{1-K} M \cdot 2^{-m_n}$$

avec

$$K = 2^{n_e - 1} - 1$$

,

— Si  $E \in [1, 2^{n_e} - 2]$ , alors nous avons une représentation normalisée et

$$v = (-1)^S \cdot 2^{E-K} (1 + M \cdot 2^{-m_n})$$

avec

$$K = 2^{n_e - 1} - 1$$

#### 1.6.3 Exemple de la représentation en virgule flottante binary-16

Dans cette partie, on se propose de regarder un peu plus en détails les valeurs représentées par un standard particulier, le standard binary-16, pour le codage des réels en virgule flottante. On donne dans la table ci-dessous quelques examples de représentations binaires binary-16 ainsi que la valeur représentée. Pour rappel, dans le standard binary-16, on utilise une représentation sur 16 bits avec 1 bit de signe,  $n_e = 5$  bits pour l'exposant,  $n_m = 10$  bits pour la mantisse. Pour le codage de l'exposant, l'excès est K = 15. L'exposant peut donc prendre des valeurs dans [-14, 15]

| Rep          | résentation l | binary-16     | Valeur représentée                                | Note                        |

|--------------|---------------|---------------|---------------------------------------------------|-----------------------------|

| Signe        | Exposant      | Mantisse      |                                                   |                             |

| 0            | 00000         | $0 \cdots 0$  | +0                                                |                             |

| 1            | 00000         | $0 \cdots 0$  | -0                                                |                             |

| $\mathbf{s}$ | 00000         | $0 \cdots 01$ | $(-1)^s 2^{-14} 1 \cdot 2^{-10} = (-1)^s 2^{-24}$ | Plus petit réél dénormalisé |

| $\mathbf{S}$ | 00000         | $0 \cdots 10$ | $(-1)^s 2^{-14} 2 \cdot 2^{-10} = (-1)^s 2^{-23}$ | Second plus petit réel      |

| $\mathbf{s}$ | 00000         | $1 \cdots 11$ | $(-1)^s(2^{-14}-2^{-24})$                         | Plus grand réel dénormalisé |

| $\mathbf{s}$ | 00001         | $0 \cdots 00$ | $(-1)^s 2^{1-15} = (-1)^s 2^{-14}$                | Plus petit réel normalisé   |

| S            | 11110         | $1 \cdots 11$ | $(-1)^s 2^{15} (2 - 2^{-10})$                     | Plus grand réel normalisé   |

| $\mathbf{S}$ | 11111         | $0 \cdots 00$ | $(-1)^s \infty$                                   |                             |

| X            | 11111         | $M, M \neq 0$ | NaN (sNan ou qNan)                                | Exception, e.g $0/0$ ,      |

TABLE 1.2 – Quelques exemples de représentation binaire du standard binary-16 de la norme IEEE-754 et de la valeur représentée. Dans les représentations binaires, le chiffre "x" indique 0 ou 1 indifféremment, i.e. signifie que la valeur de ce chiffre n'est pas pris en compte.

Pour donner un ordre de grandeur en base  $10: 2^{-24} \approx 6.10^{-8}, 2^{15}(2-2^{-10}) = 65504.$

#### 1.7 Représentation des caractères

En informatique, une information est codée exclusivement par des séquences de 0 et 1. On a vu précédemment comment coder des entiers et des réels en binaire mais on a également besoin de trouver un moyen de coder du texte (caractères '0', '1', 'A', 'é'; ponctuation!,? espace, ...; symboles spéciaux comme €, \$, @) comme une séquence de 0 et 1. Pour coder/décoder des caractères, il faut se mettre d'accord sur le nombre de bits utilisés pour représenter un caractère (pour pouvoir ségmenter une longue séquence de 0 et de 1 en caractères) et sur une table associant un mot binaire à un caractère. Dans les années 1980-1990, il y avait plusieurs normes pour coder les

caractères qui sont apparues à travers le monde : l'ASCII aux Etat-unis, le KOI8-R en Russie, ... Ces normes proposaient d'encoder les caractères sur 7 ou 8 bits mais le fait que les normes soient nées indépendemment les unes des autres rendait les systèmes difficilement interopérables et très spécifiques (en Russe, il faut pouvoir représenter l'alphabet cyrillique). Par exemple, l'ASCII (American Standard Code for Information Interchange) développé aux Etat-Unis, utilise 7 bits (128 valeurs possibles) pour coder des caractères dont les codes apparaissent sur la table suivante <sup>7</sup>.

| b7          | 0 0                    | 0                   | 0           | 1 1 1                                                                                          |

|-------------|------------------------|---------------------|-------------|------------------------------------------------------------------------------------------------|

| b6          | 0 0                    | 1                   | 1           | 0 0 1 1                                                                                        |

| b5          | 0 1                    | 0                   | 1           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                          |

| BITS        | •                      |                     | •           |                                                                                                |

|             | CONTROL                | SYM                 | BOLS        | LIDDED CACE LOWED CACE                                                                         |

|             | CONTROL                | NUM                 | BERS        | UPPER CASE LOWER CASE                                                                          |

| b4 b3 b2 b1 |                        |                     | 22.10       |                                                                                                |

|             | 0 16                   | 32                  | 48          | 64 80 96 112 n                                                                                 |

| 0 0 0 0     | NUL DLE                |                     |             |                                                                                                |

|             | 0 0 10 20<br>1 17      | 20 40<br>33         | 30 60<br>49 | 60 40 100 50 120 60 140 70 160<br>65 81 97 113                                                 |

| 0 0 0 1     | SOH DC1                | !                   | 1           | A Q a q                                                                                        |

| 0 0 0 1     |                        |                     |             | 61 41 101 51 121 61 141 71 161                                                                 |

| -           | 2 18                   | 34                  | 50          | 66 82 98 114                                                                                   |

| 0  0  1  0  | STX DC2                | "                   | 2           | B R b r                                                                                        |

|             | 2 2 12 22<br>3 19      | 22 42<br>35         | 32 62<br>51 | 62 42 102 52 122 62 142 72 162<br>67 83 99 115                                                 |

| 0 0 1 1     |                        | 11                  | 1 2         |                                                                                                |

| 0 0 1 1     | 3 3 13 23              | 23 43               | 33 63       | 63 43 103 53 123 63 143 73 163<br>68 84 100 116                                                |

|             |                        |                     | 52          |                                                                                                |

| 0  1  0  0  | EOT DC4                | \$                  | 4           | D   T   d   t                                                                                  |

|             | 4 4 14 24              | 24 44               | 34 64       | 64     44     104     54     124     64     144     74     164       69     85     101     117 |

| 0 1 0 1     | <sup>®</sup> ENQ   NAK |                     | 5           | E S U T e T u                                                                                  |

| 0 1 0 1     | 5 5 15 25              | / <b>0</b><br>25 45 |             |                                                                                                |

|             | 6 22                   | 38                  | 54          | 70 86 102 118                                                                                  |

| 0  1  1  0  | ACK SYN                | &                   | 6           | F V f v                                                                                        |

|             | 6 6 16 26<br>7 23      | 26 46               |             | 66 46 106 56 126 66 146 76 166                                                                 |

| 0 1 1 1     | BEL ETB                | 39                  | 7           | G W 103 119 W                                                                                  |

| 0 1 1 1     | 7 7 17 27              | 27 47               | 37 67       | 67 47 107 57 127 67 147 77 167                                                                 |

|             | 8 24                   | 40                  | 56          | 72 88 104 120                                                                                  |

| 1 0 0 0     | BS CAN                 | (                   | 8           | H   X   h   x                                                                                  |

|             |                        | 28 50               |             | 70 48 110 58 130 68 150 78 170                                                                 |

| 1 0 0 1     | <sup>9</sup> HT EM     | 41                  | 9           | 73   89   105   121   V                                                                        |

| 1 0 0 1     | 9 11 19 31             | ) 51                | 39 71       |                                                                                                |

|             | 10 26                  | 42                  | 58          | 74 90 106 122                                                                                  |

| 1  0  1  0  | LF SUB                 | *                   | :           | J                                                                                              |

|             | A 12 1A 32             |                     | 1           | 72 4A 112 5A 132 6A 152 7A 172                                                                 |

| 1 0 1 1     | VT ESC                 | 43<br>_L            | 59          | 75   91   107   123   123   {                                                                  |

| 1 0 1 1     | B 13 1B 33             | +<br>2B 53          | 3B 73       | 73 4B 113 5B 133 6B 153 7B 173                                                                 |

| -           | 10 00                  | 44                  | 60          | 76 92 108 124                                                                                  |

| 1  1  0  0  | FF S FS                | ,                   | <           |                                                                                                |

|             | C 14 1C 34             | 2C 54               | 3C 74       | 74 4C 114 5C 134 6C 154 7C 174                                                                 |

| 1 1 0 1     | 13 CD CC               | 45                  | 61          | 77 93 109 125                                                                                  |

| 1 1 0 1     | CR GS 35               | 2D 55               | 3D 75       | 75 4D 115 5D 135 6D 155 7D 175                                                                 |

|             | 14 30                  | 46                  | 62          | 78 94 110 126                                                                                  |

| 1 1 1 0     | SO RS                  |                     | >           | N ^ n ~                                                                                        |

|             | E 16 1E 36             | 2E 56               |             | 76 4E 116 5E 136 6E 156 7E 176                                                                 |

|             | 15 31                  | 47                  | 63          | 79 95 111 127                                                                                  |

| 1 1 1 1     | SI US 37               | 2F 57               | ?<br>3F 77  | 77 4F 117 5F 137 6F 157 7F 177                                                                 |

|             | r 11 1F 37             | 2F 57               | 13F 77      | 11 4F 111 0F 101 0F 101 (F 177                                                                 |

LEGEND:

CHAR

Victor Eijkhout Dept. of Comp. Sci. University of Tennessee Knoxville TN 37996, USA

<sup>7.</sup> La table ASCII est produite par Victor Eijkhout

1.8. UN EXEMPLE 15

Vous l'aurez remarqué, il nous manque nos caractères accentués; en effet, les américains n'utilisent pas de caractères accentués; et bien sûr bien d'autres caractères manquent pour satisfaire toutes les langues. Il y a eu donc une flopée de normes dont notamment les normes ISO-8859-x, avec x variant de 1 à 16, chacune encodant des caractères d'une langue différente, sur 8 bits. Par exemple, la norme ISO 8859-1 couvre les caractères de la plupart des langues européennes, la norme ISO 8859-5 couvre l'alphabet cyrillique, ... Les normes ISO étendent la norme ASCII en utilisant les mêmes 128 premiers caractères. Comme la norme ISO propose un encodage sur 8 bits, il y a 128 caractères supplémentaires à utiliser. En pratique ces 128 caractères supplémentaires ne sont pas tous utilisés mais en tout cas, en fonction de la norme considérée, ils ne représentent pas la même valeur; Quelques caractères des différentes normes ISO-8859-x sont représentés sur la figure 1.2.

| Code     | numé | rique |     |    |   |   |   | Nu | mér | o de | pa | rtie | d'Is | 8 08 | 859 |    |    |    |

|----------|------|-------|-----|----|---|---|---|----|-----|------|----|------|------|------|-----|----|----|----|

| binaire  | Oct  | Déc   | Hex | 1  | 2 | 3 | 4 | 5  | 6   | 7    | 8  | 9    | 10   | 11   | 13  | 14 | 15 | 16 |

|          |      |       | 2   |    |   |   |   |    |     |      |    |      |      |      |     |    |    |    |

| 11100010 | 342  | 226   | E2  | â  | â | â | â | т  | ق   | β    | ì  | â    | â    | ١    | ā   | â  | â  | â  |

| 11100011 | 343  | 227   | E3  | ã  | ă |   | ã | у  | ك   | γ    | 7: | ā    | ā    | 1    | ć   | ã  | ā  | ā  |

| 11100100 | 344  | 228   | E4  | ä  | ä | ä | ä | ф  | J   | δ    | a: | ä    | ä    | ٦    | ä   | ä  | ä  | ä  |

| 11100101 | 345  | 229   | E5  | å  | ſ | ċ | å | x  | p   | 3    | E  | å    | å    | ٦    | å   | å  | å  | ć  |

| 11100110 | 346  | 230   | E6  | æ  | ć | ĉ | æ | ц  | ن   | ζ    | r. | æ    | æ    | 9    | ę   | æ  | æ  | æ  |

| 11100111 | 347  | 231   | E7  | ç  | ç | ç | i | ч  | ٥   | η    | n. | ç    | i    | er.  | ê   | ç  | ç  | ç  |

| 11101000 | 350  | 232   | E8  | è  | č | è | č | ш  | 9   | θ    | υ  | è    | č    | ۲    | č   | è  | è  | è  |

| 11101001 | 351  | 233   | E9  | é  | é | é | é | щ  | ی   | t    | 1  | é    | é    | 8    | é   | é  | é  | é  |

| 11101010 | 352  | 234   | EA  | ê  | ę | ê | ę | ъ  | ي   | к    | 1  | ê    | ę    | -    | ź   | ê  | ê  | ê  |

| 11101011 | 353  | 235   | EB  | ĕ  | ë | ë | ë | ы  | ÷   | λ    | Ď. | ë    | ë    | *    | ė   | ë  | ë  | ë  |

| 11101100 | 354  | 236   | EC  | Ť  | ě | ì | ė | ь  |     | μ    | 7  | ì    | ė    | •    | ģ   | Ť  | 1  | ì  |

| 11101101 | 355  | 237   | ED  | f  | f | í | ĭ | э  | æ   | ν    | D  | f    | f    | ٠    | ķ   | ť  | f  | ĭ  |

| 10101101 | 255  | 173   | AD  | Г  |   |   |   | 2  | SHY |      |    |      |      | ญ    |     | Si | ΙΥ |    |

| 10101110 | 256  | 174   | AE  | ®  | Ž |   | Ž | ÿ  |     |      | ®  | ®    | Û    | ม    | ®   | ®  | ®  | ź  |

| 10101111 | 257  | 175   | AF  | 37 | ż | ż |   | п  |     | _    | =: | 15   | n    | ภ    | Æ   | Ÿ  | -  | ż  |

FIGURE 1.2 – Extrait des normes ISO-8859-x disponibles. Source : https://fr.wikipedia.org/wiki/ISO\_8859.

Plus récemment, un nouveau format, issu du standard Unicode et de la norme ISO 10646, commence à s'imposer : le format UTF-8. Ce format code tout les caractères possibles en utilisant un nombre variable de mots de 8 bits (le format UTF-8 accepte jusqu'à 4 octets).

## 1.8 Un exemple

Pour terminer cette partie, j'aimerais revenir sur la différence entre une valeur et son représentant. Si on considère la séquence binaire ci-dessous (représentée en hexadécimal pour rester compact) :

$$(626F6E6A6F757221)_{16}$$

elle peut représenter plusieurs valeurs :

- la chaîne de caractères "bonjour!" si je considère que la séquence représente des caractères codés en ASCII

- la valeur 7 093 009 341 547 377 185 si je considère que la séquence représente un entier codé sur 64 bits

- l'image si je considère que chaque bloc de 8 bits code le niveau de gris d'un pixel considéré comme noir pour 0 et blanc pour 255,

— ...

## Chapitre 2

# La couche physique et la couche logique

Nous venons de voir comment coder des informations en binaire. Nous allons ici nous intéresser à la manière de manipuler ces représentations et notamment proposer des algorithmes permettant d'effectuer des opérations arithmétiques sur les représentations binaires des nombres. Pour le moment, on ne sait faire ces opérations que sur le papier mais, pour automatiser des calculs, il faut mettre au point des mécanismes physiques (mécaniques, électroniques, optiques) réalisant ces opérations. On commencera par introduire le transistor qui est l'élément majeur des circuits électroniques que nous allons présenter <sup>1</sup> et très vite, nous en ferons l'abstraction en introduisant les portes logiques à partir desquelles nous élaborerons différents circuits particuliers qui nous permettrons de construire notre première architecture.

#### 2.1 Un peu d'électronique

Avant de voir plus en détails comment se construit un ordinateur, il faut introduire quelques éléments d'électronique pour comprendre comment représenter physiquement un bit ainsi que des circuits électroniques permettant de manipuler ces signaux. Ces circuits vont principalement reposer sur le transistor et nous allons voir pourquoi ce composant est particulièrement bien adapté.

#### 2.1.1 Niveaux logiques et valeurs de tension

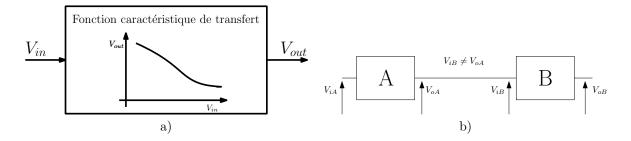

La représentation d'un bit se fait en électronique par des niveaux de tension. Disons  $^2$ , par exemple, 0V pour un bit au niveau bas b=0 et 1V pour un bit au niveau haut b=1. Cela étant dit, quel est l'état binaire d'une tension à 0.75 V? probablement b=1; 0.25 V? probablement b=0 et qu'en est-il de 0.49V et 0.51V? A cause des défauts de fabrication, des perturbations possibles de l'environnement du circuit, il est nécessaire d'introduire des tolérances et de définir des domaines de tension acceptable pour définir chacun des niveaux logiques. Les circuits électroniques que nous allons considérer vont transformer des tensions d'entrées  $V_{in}$  en des tensions de sortie  $V_{out}$  (fig. 2.1a) et la fonction reliant les deux est appelée fonction caractéristique de transfert (Voltage Transfer Characteristics).

Les fabricants définissent des domaines pour les entrées et sorties dans lesquels ils garantissent le fonctionnement de leur circuit :

- pour les entrées :

- $-v_{il}$ : tension maximale d'entrée pour que le composant la considère à l'état bas  $b_{in}=0$

- $-v_{ih}$ : tension minimale d'entrée pour que le composant la considère à l'état haut  $b_{in}=1$

- pour les sorties :

<sup>1.</sup> Un microprocesseur des années 1970 comptait quelques milliers de transistor. En 2015, les microprocesseurs multi-coeurs contiennent une dizaine de milliards de transistors (10.10<sup>9</sup>). Source: https://en.wikipedia.org/wiki/Transistor.count

<sup>2.</sup> Les circuits logiques utilisent généralement des tensions entre 0V et 3.3V ou entre 0V et 5V. On utilise ici 1V à titre d'illustration.

FIGURE 2.1 – a) Vision schématique d'un circuit transformant une tension  $V_{in}$  en une tension  $V_{out}$ . La fonction reliant les deux est la fonction caractéristique de transfert. b) Des marges de bruit doivent être introduites pour garantir le bon fonctionnement de composants interconnectés.

- $v_{ol}$ : tension maximale de sortie que le composant produit pour une sortie à l'état bas  $b_{out}=0$

- $v_{oh}$  : tension minimale de sortie que le composant produit pour une sortie à l'état haut  $b_{out}=1$

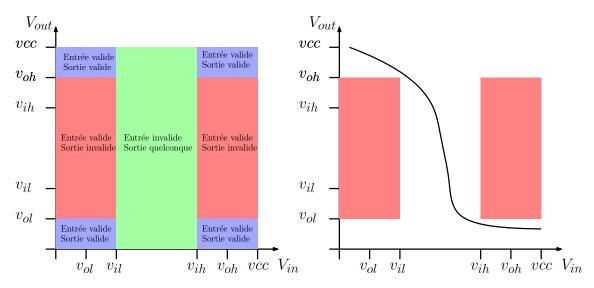

Quelle que soit la fonction réalisée par le circuit, le fabricant garantie que si l'entrée représente un état binaire valide  $(V_{in} \in [0, v_{il}] \cup [v_{ih}, V_{cc}])$ , alors la sortie représentera un état binaire valide  $(V_{out} \in [0, v_{ol}] \cup [v_{oh}, V_{cc}])$ . Par ailleurs, pour prendre en compte les imperfections de son circuit, les tolérances de sortie sont plus strictes que les tolérances d'entrée : une sortie est considérée à l'état haut si  $v_{out} \geq v_{oh} > v_{ih}$  et à l'état bas si  $v_{out} \leq v_{ol} < v_{il}$ . En effet, considérons que nous interconnections deux composants comme sur la figure 2.1b. Différentes sources de bruit dûes à l'environnement du circuit conduisent au fait que le potentiel de sortie  $V_{oA}$  est différent du potentiel d'entrée  $V_{iB}$ . Le potentiel de sortie  $V_{oA}$  ne doit pas être vu comme un potentiel constant mais comment étant perturbé par un certain bruit. Si on définit  $v_{ol} = v_{il}$ , et que  $V_{oA} = v_{ol}$ , i.e. la tension maximale pour indiquer un niveau logique bas en sortie de A, la perturbation peut conduire à ce que ce niveau bas soit considéré comme invalide pour le composant B. C'est donc pour garantir qu'une sortie valide demeure une entrée valide, malgré le bruit de transimission, qu'on impose à ce que  $v_{ol} < v_{il}$  et  $v_{oh} > v_{ih}$ . Les différences  $v_{il} - v_{ol}$  et  $v_{oh} - v_{ih}$  sont appelées marges de bruit. Il y aurait beaucoup d'autres choses à dire sur la compatibilité des circuits interconnectés mais nous nous arrêterons là dans ce cours et je vous renvois vers un cours d'électronique pour en savoir plus.

FIGURE 2.2 — Les domaines interdits pour la fonction caractéristique de transfert sont représentés en rouge. Quelle que soit la fonction réalisée par le circuit, la fonction caractéristique de transfert devra toujours éviter les domaines interdits pour s'assurer qu'une entrée valide donne toujours une sortie valide. La fonction représentée en noir est une fonction valide.

Pour en revenir à un seul composant, notez que rien n'interdit de produire une sortie valide si l'entrée est invalide. Cela conduit ainsi à définir des domaines interdits pour la fonction caractéristique de transfert comme illustré sur la figure 2.2, domaines dans lesquels il est interdit de faire passer la fonction de transfert caractéristique.

Raisonner avec la fonction caractéristique de transfert permet d'identifier une caractéristique des circuits permettant de manipuler des "représentations binaires" : ce circuit doit utiliser des composants non linéaires. Au début de l'informatique, dans les années 1930-1940, on utilisait des relais électromécaniques comme par exemple le relais de Joseph Henry illustré sur la figure 2.3.

FIGURE 2.3 – Relai électromécanique de Joseph Henry. Branchons  $v_{out}$  sur la patte 1,  $v_{cc}$  sur la patte 4, la masse sur la patte 5 et  $v_{in}$  sur la bobine, on obtient alors un inverseur. Si  $v_{in}=0$ , la languette métallique 10 relie la patte 1 à la patte 4 donc  $v_{out}=v_{cc}$ . Si  $v_{in}=v_{cc}$ , le champ magnétique de la bobine conduit à placer la languette métallique 10 en contact avec la pièce 12 et donc  $v_{out}=0$ . Illustration de http://history-computer.com.

En pratique, les relais sont encombrants, sujets aux interférences, peu robustes dans le temps puisque mécaniques, gourmands en énergie, ... Dans les années 1950 est apparu le transistor, un interrupteur électronique commandable qui a révolutionné l'informatique.

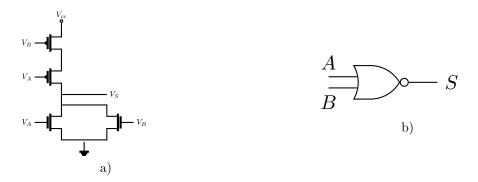

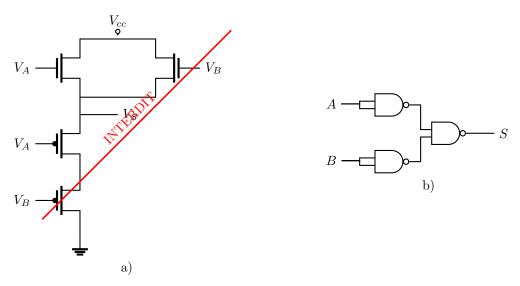

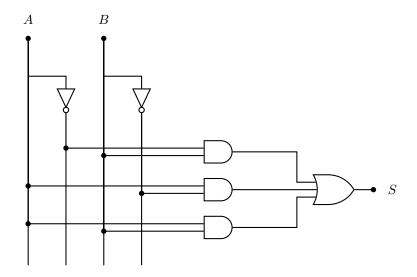

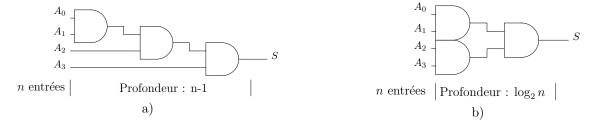

#### 2.1.2 Transistors CMOS et inverseur

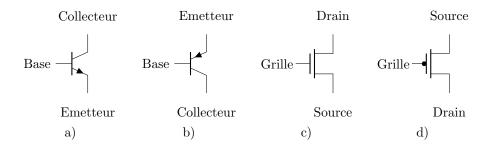

Comme nous venons de le voir, il nous faut disposer d'un composant électronique dont la fonction caractéristique de transfert est non linéaire. Le transistor, apparu dans les années 1950 est justement un composant non linéaire. Il existe plusieurs technologies pour réaliser des transistors (TTL, MOS, ..) et ce n'est pas le sujet de ce cours que de les présenter. On ne s'intéressera qu'à une technologie : le transistor MOSFET (Metal Oxyde Field Effect Transistor) et on va s'abstraire du transistor en le voyant comme un interrupteur commandable. Des transistors TTL et MOS sont représentés sur la figure 2.4 et les transistors MOS sont ceux représentés sur les figures 2.4c, d. Je vous renvois vers un cours de physique des semi-conducteurs pour comprendre le fonctionnement de ces transistors. Nous retiendrons ici deux états de fonctionnement du transitor (passant/saturé ou bloqué) et que l'état dans lequel se trouve le transistor dépends de la différence de potentiel entre la grille et la source.

Pour ce qui nous concerne dans ce cours, un transistor est abstrait comme un interrupteur commandable (fig. 2.5a):

FIGURE 2.4-a) Transistor bipolaire NPN. b) Transistor bipilaire PNP. c) Transistor unipolaire NMOS. d) Transistor unipolaire PMOS