Architecture des ordinateurs

Mémoires, périphériques et interruptions

CentraleSupélec

2025-11-23

Au menu

Cours

- les mémoires et la mémoire cache

- les périphériques : quoi ? canal d’échange, protocole d’échange, prise en compte par interruption

TP

- TP : Interruptions : écoute passive des périphériques

- TP : ordonnanceur : exécuter plusieurs programmes en parallèle avec un chemin de données

- TP Bonus : place au jeu !

Mémoires

Caractéristique des mémoires

Caractéristiques

- Mode d’accès : aléatoire (RAM), séquentiel (disque dur), associatif (cache)

- Capacité d’écriture : ROM (en lecture seule), \(\overline{\mathtt{ROM}}\) (en lecture et écriture)

- volatilité : maintien des informations en l’absence de courant ? (ROM : forcément non volatile, RAM : ça dépend; SDRAM : volatile ; NVRAM : non volatile ou RAM + pile : CMOS)

Les mémoires mortes : non volatiles, en lecture seule (\(\approx\))

- ROM : Read Only Memory (programmée à la fabrication)

- PROM : Programmable Read Only Memory (fusibles; programmable une fois)

- EPROM : Erasable Programmable Read Only Memory (Ultraviolet)

- EEPROM : Electrically Programmable Read Only Memory (e.g. pour contenir le BIOS : Basic Input Output System; les paramètres sont mémorisés avec une RAM volatile + batterie)

Les mémoires en lecture/écriture : Volatiles, accès aléatoire

- Registres : bascules D maître/esclave

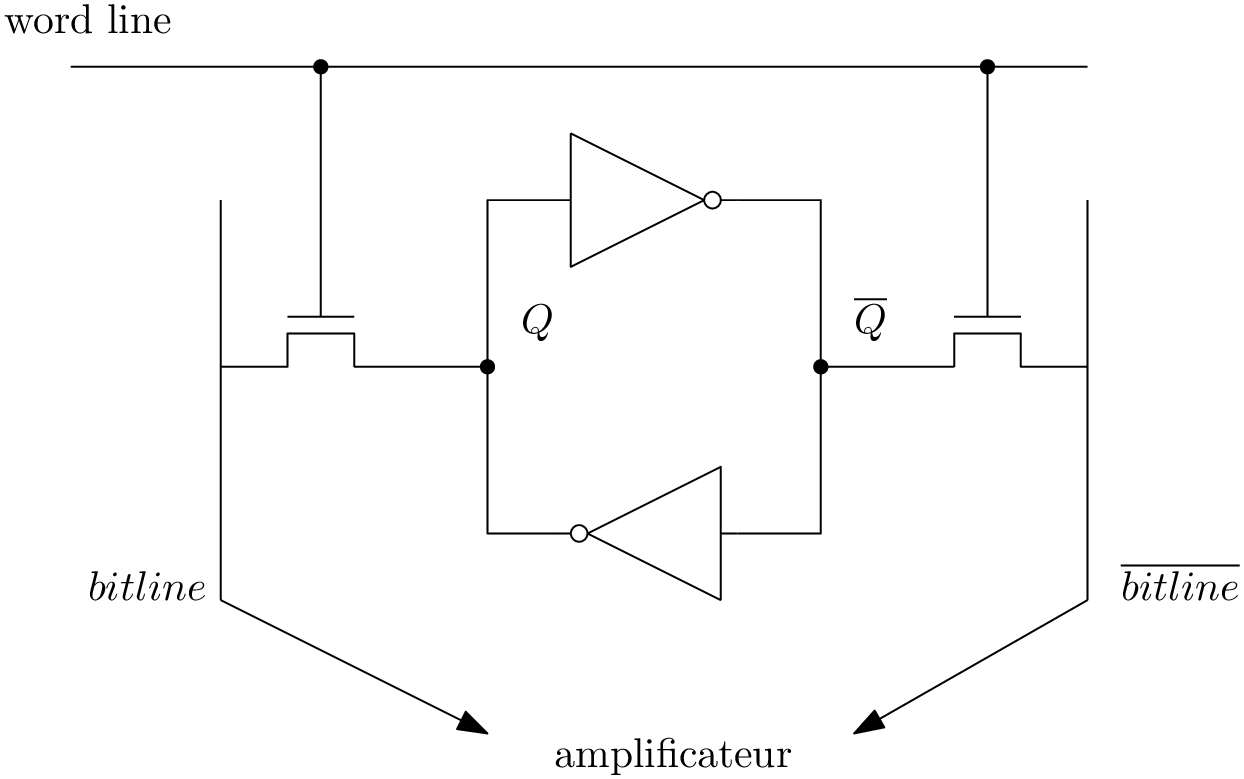

- Static RAM (SRAM)

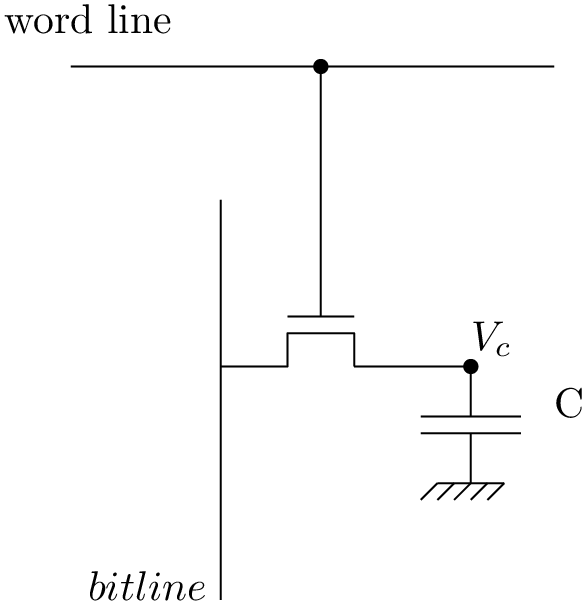

- Dynamic RAM (DRAM)

Les mémoires en lecture/écriture : non-Volatiles

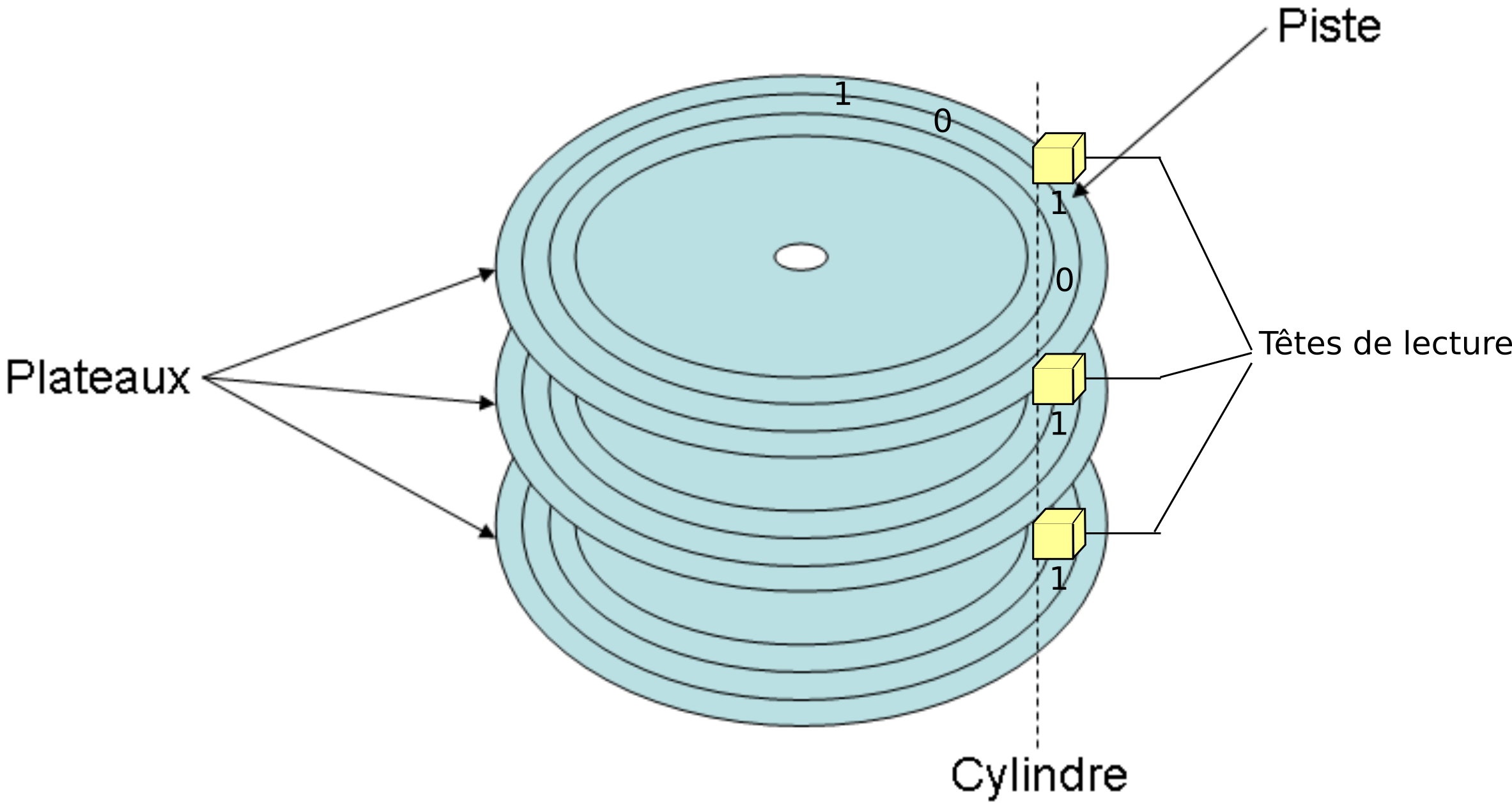

- accès séquentiel : Disques durs magnétiques

- accès aléatoire : disques durs SSD, mémoire flash, nvSRAM, ..

Les mémoires vives

Capacité : \(\approx\) 32-64 bits

Temps d’accès : \(\approx\) 1 ps (\(10^{-12}s\))

Volatile

Les mémoires vives

Capacité : 10 Ko - 10 Mo

Temps d’accès : \(\approx\) 1ns

Volatile

Les mémoires vives

Capacité : 10 Go

Temps d’accès : 80 ns (réécriture toutes les ms)

Volatile

Les mémoires de masse

Capacité : 1 To

Temps d’accès : 10 ms

Non volatile

Synthèse des mémoires vives et de masse

Compromis ?

| Type | Capacité | Latence | Coût (au Gi-octet) |

|---|---|---|---|

| Registre | 100 bits | 20 ps | très cher |

| SRAM | 10 Ko - 10 Mo | 1-10 ns | ≈ 1000 € |

| DRAM | 10 Go | 80 ns | ≈ 10 € |

| Flash | 100 Go | 100 μs | ≈ 1 € |

| Disque dur Magn | 1 To | 10 ms | ≈ 0.1 € |

Une mémoire rapide et de grosse capacité ??

Mémoire cache

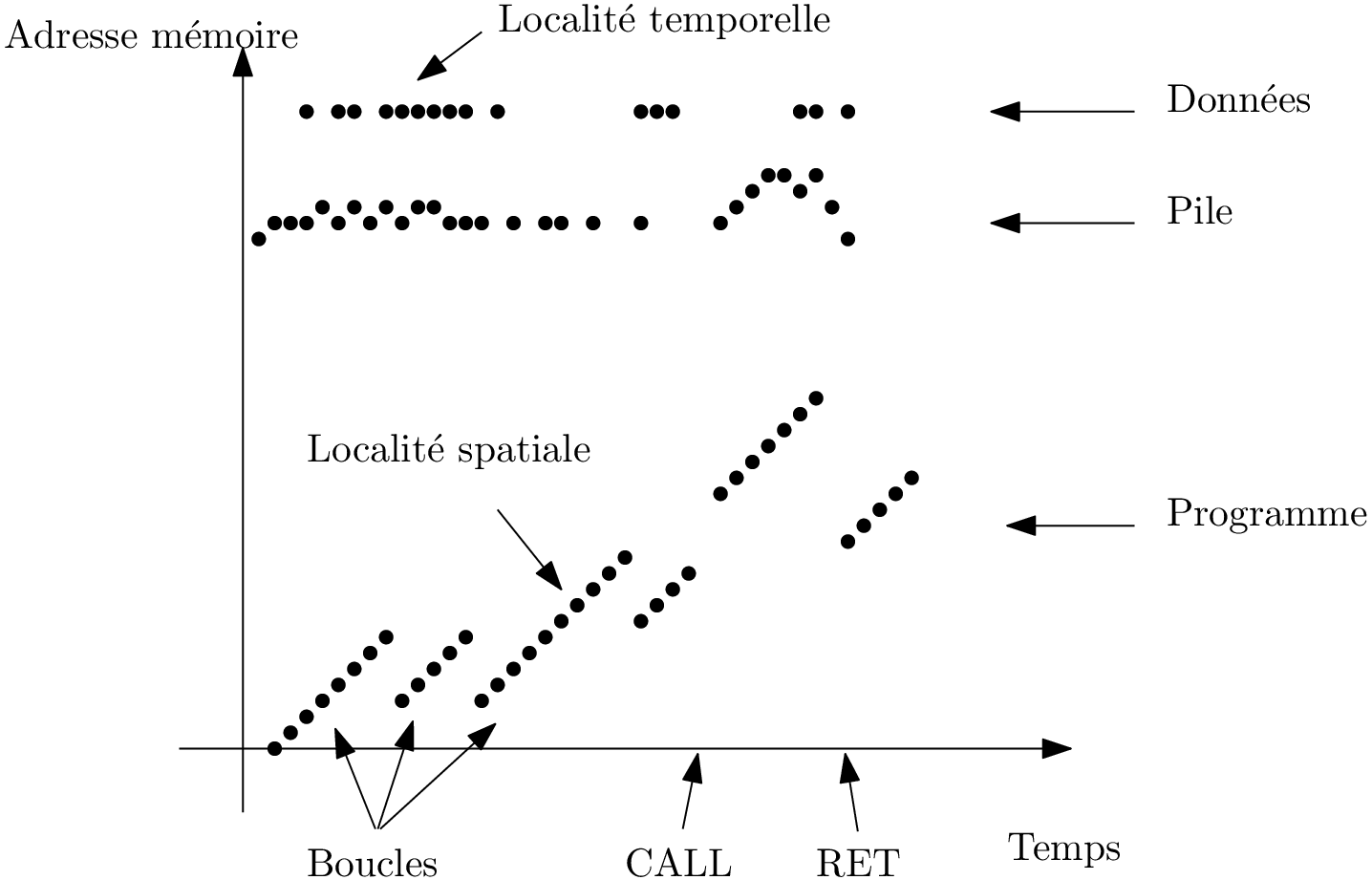

La clé : le principe de localité

Idée: combiner une petite mémoire rapide avec une grosse mémoire lente

- Localité temporelle : on charge en mémoire rapide une donnée à laquelle on accède

- Localité spatiale : on charge aussi les voisines

Problème de doublons ? Politique de remplacement ? Dépends de la réalisation…

Réalisation matérielle: principe de fonctionnement d’un cache

Principe

A partir d’une petite information (clé), on retrouve le reste (valeur).

Analogie : annuaire téléphone

En pratique

L’adresse demandée est divisée en plusieurs parties dont une sert de clé.

Tableau associatif : Cache[clé] = {adr, valeur, ..}

- Si la donnée est présente en cache : valide et accès rapide

- Sinon il faut récupérer la donnée et la placer dans le cache.

Réalisations matérielles d’un cache

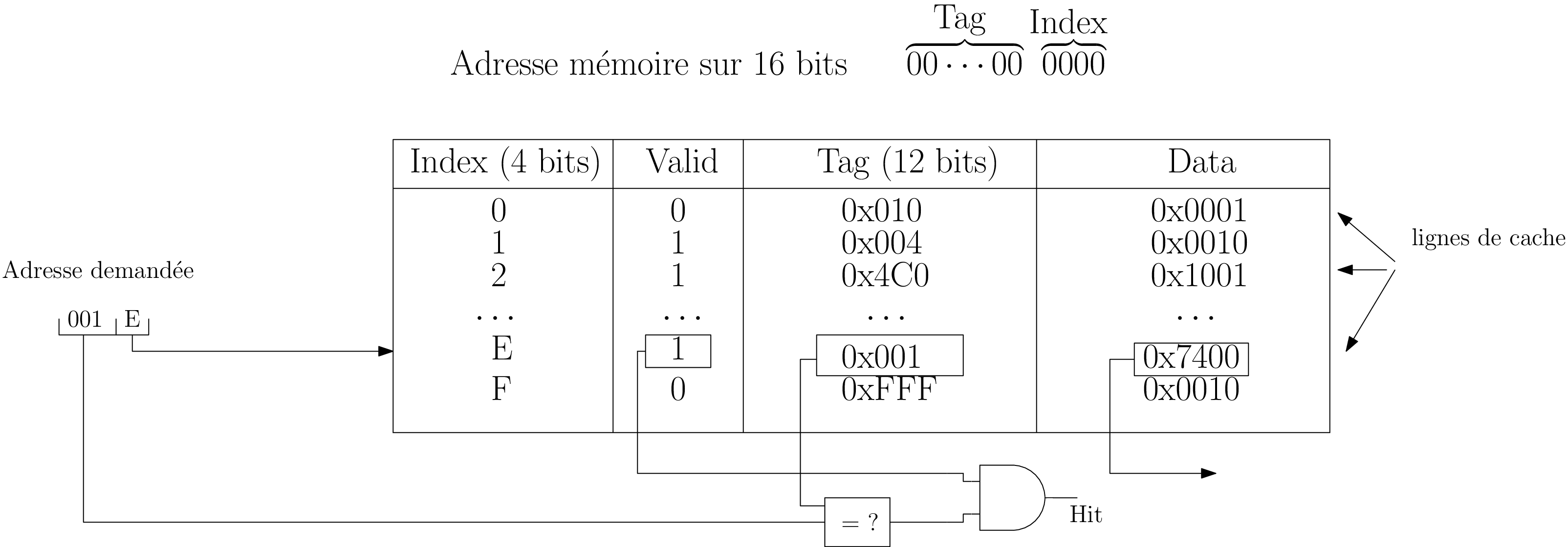

RAM[Adr] → Cache[Adr₃Adr₂Adr₁Adr₀]

pourquoi les bits de poids faibles comme index ?

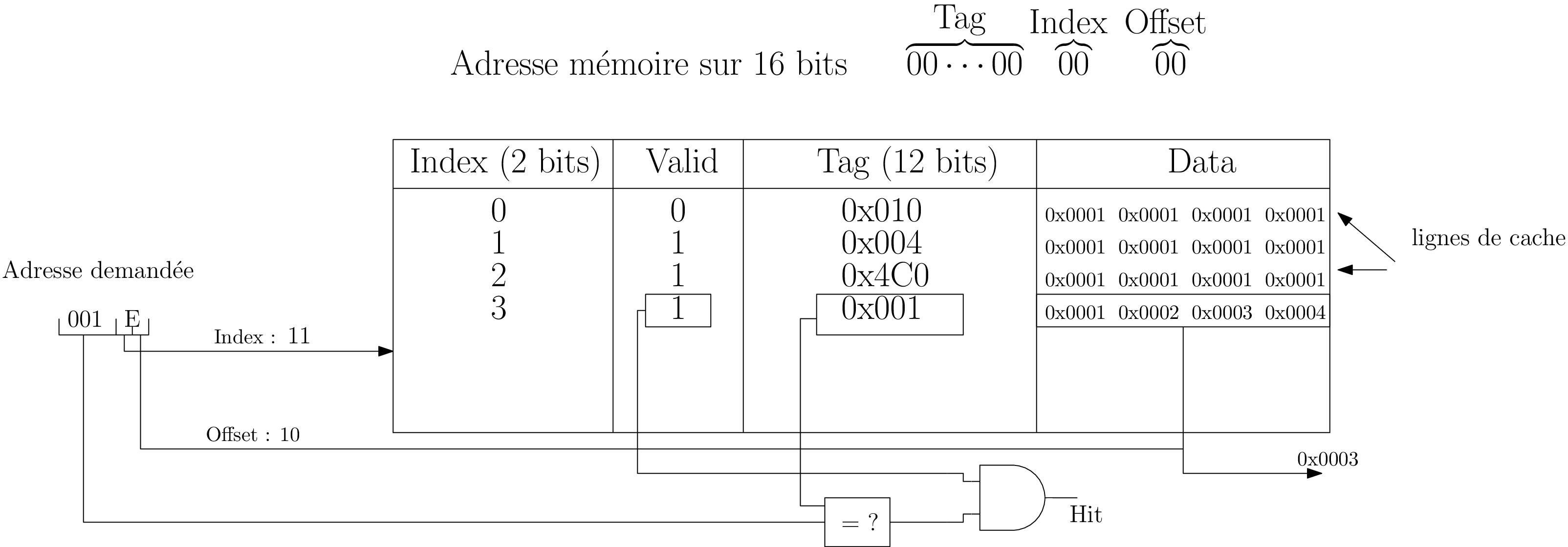

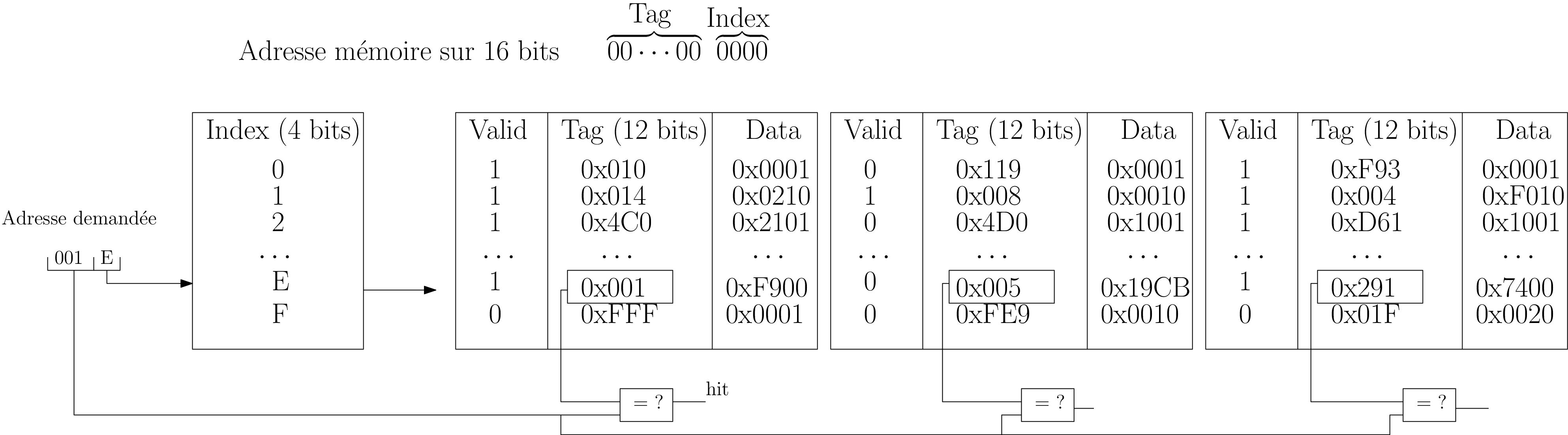

Réalisations matérielles d’un cache

Un bloc : \(2^{|offset|}\) mots;

Toutes les adresses de même “Index” ciblent la même ligne.

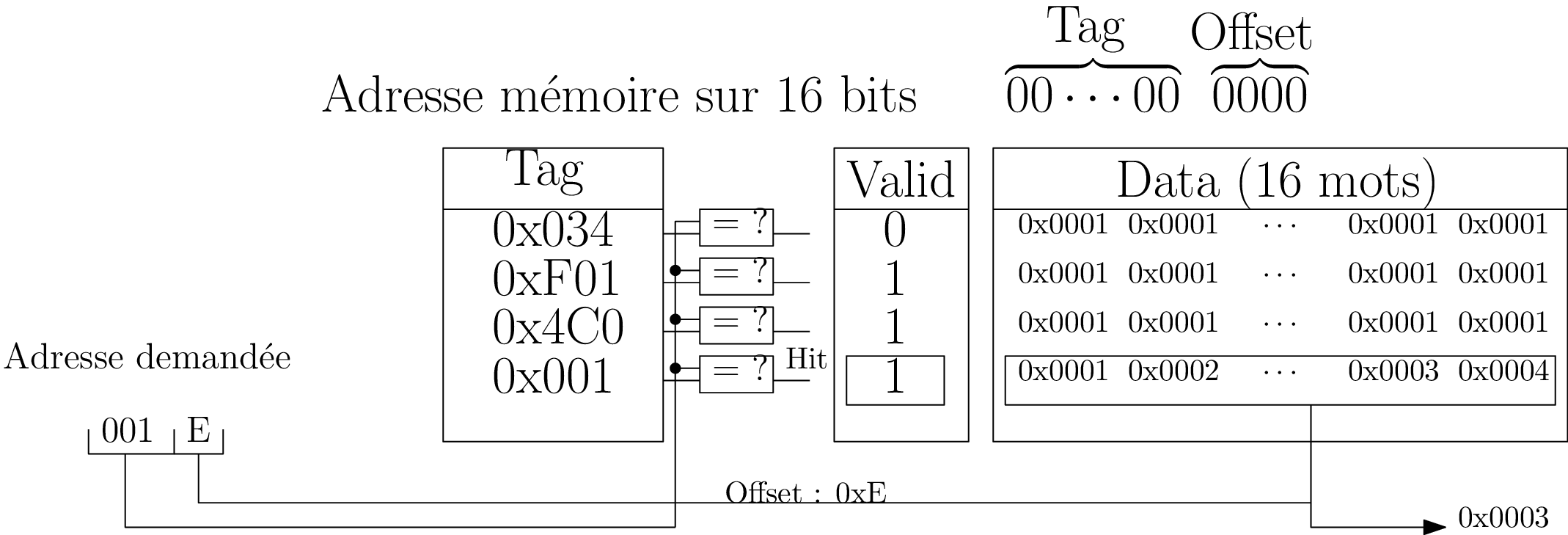

Réalisations matérielles d’un cache

Une donnée peut occuper n’importe quelle ligne de cache. Lourd matériellement.

Réalisations matérielles d’un cache

Cohérence cache/mémoire centrale

Problème

Une donnée d’une même adresse peut être à la fois en cache, mémoire centrale, voir même sur le disque (e.g. swap)

Politiques d’écriture

- Write through : propagation immédiate d’une modification vers la mémoire principale

- Write back : écriture différée; écriture au remplacement (dirty bit)

Périphériques

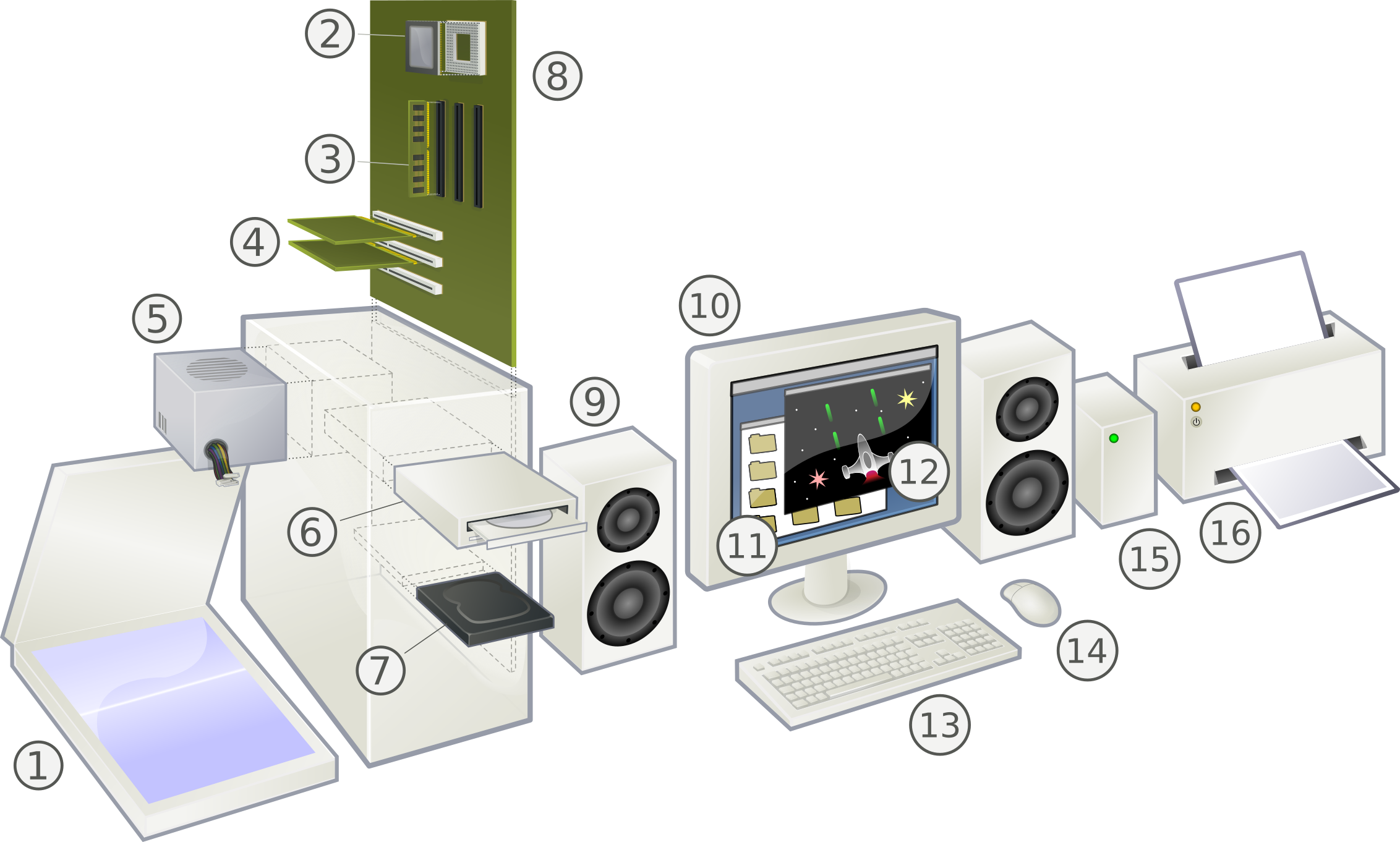

Les périphériques d’entrée/sortie

Les périphériques d’entrée/sortie

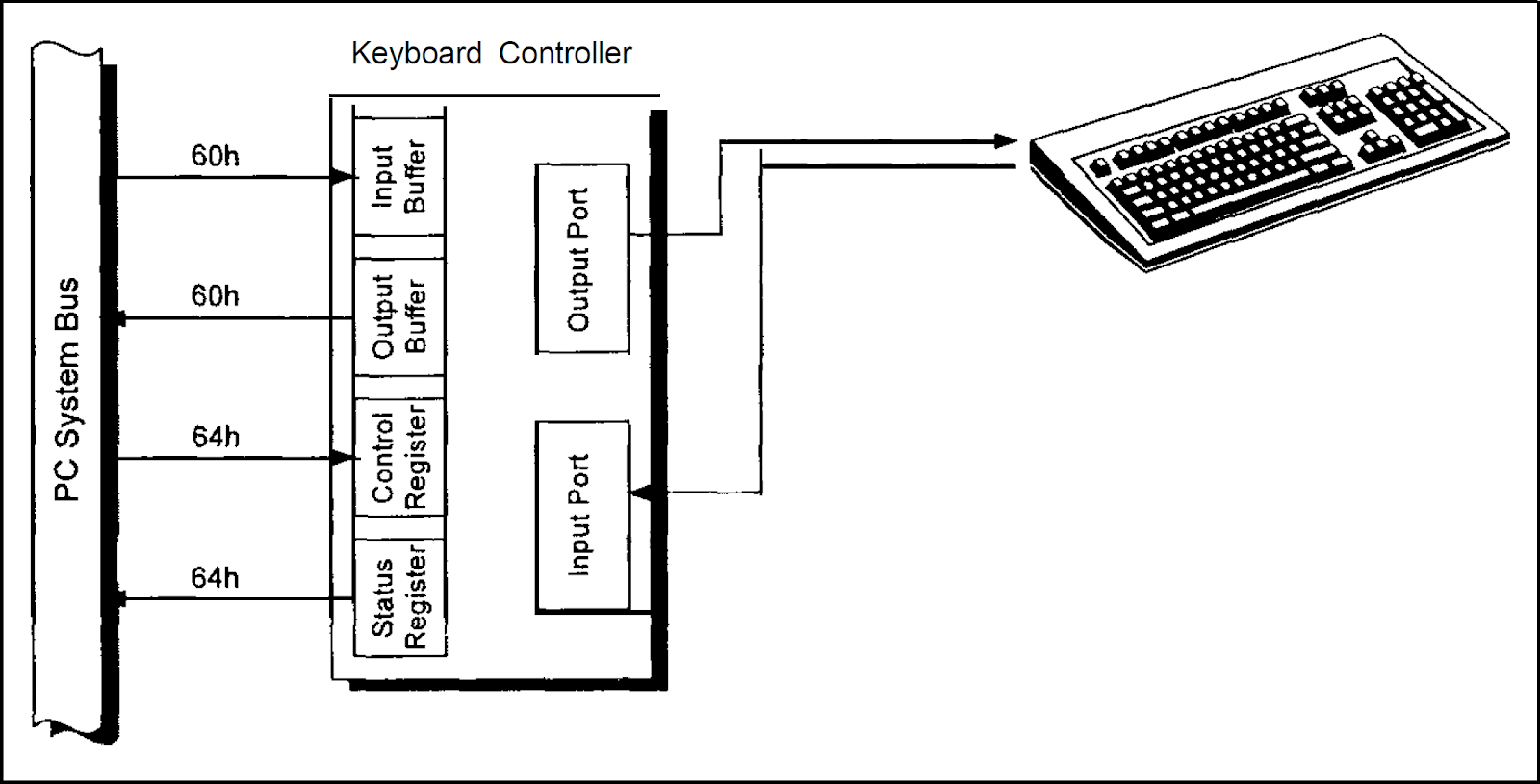

Structure d’un périphérique

Au périphérique est associé un contrôleur (e.g. contrôleur disque) qui possède :

- des registres

- des machines à état

- …

Le périphérique est couplé aux bus d’adresses, données, contrôle.

Exemple d’un contrôleur clavier (e.g. Intel 8042)

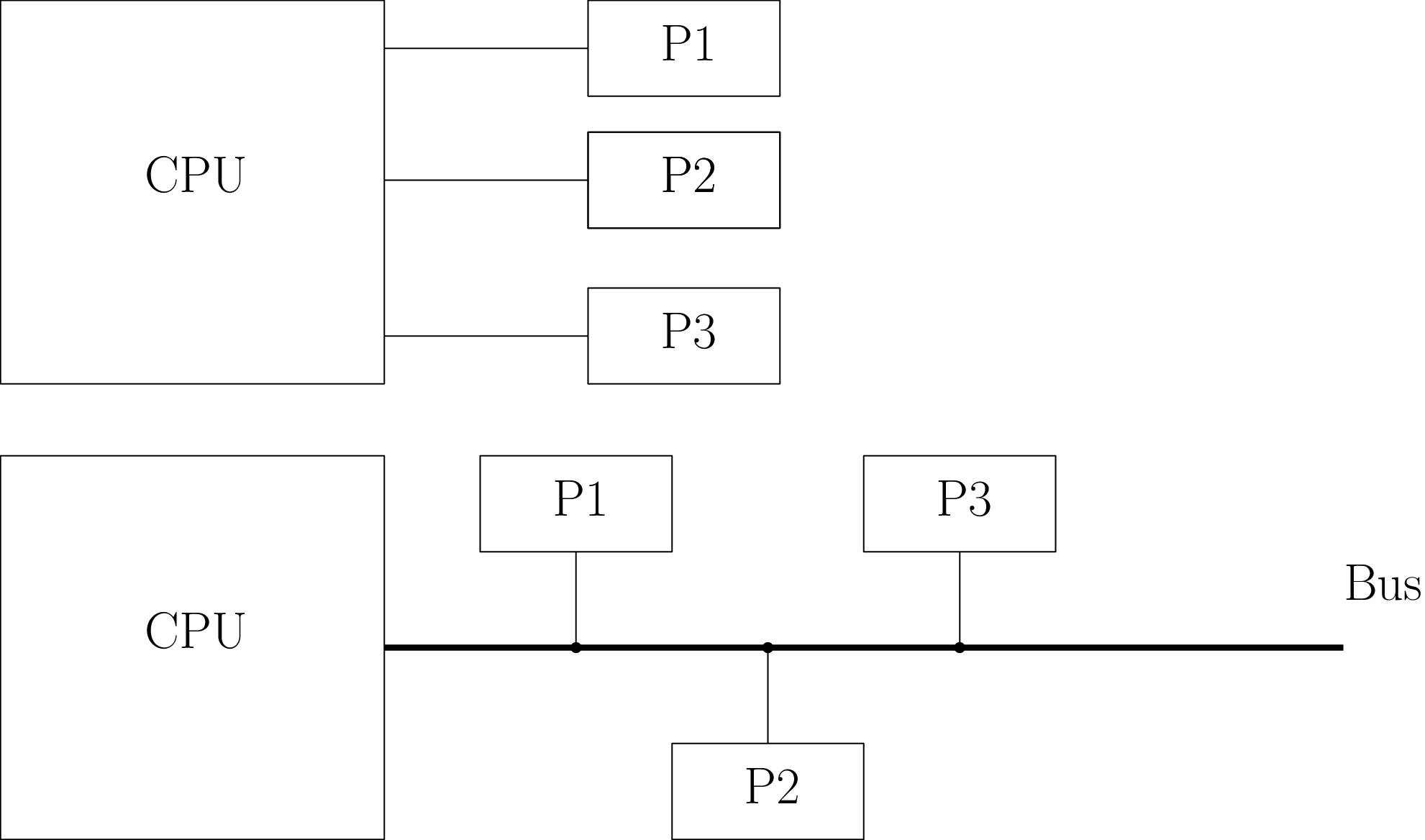

Bus : Interconnexion des périphériques et du chemin de données

Interconnexion des périphériques et du chemin de données

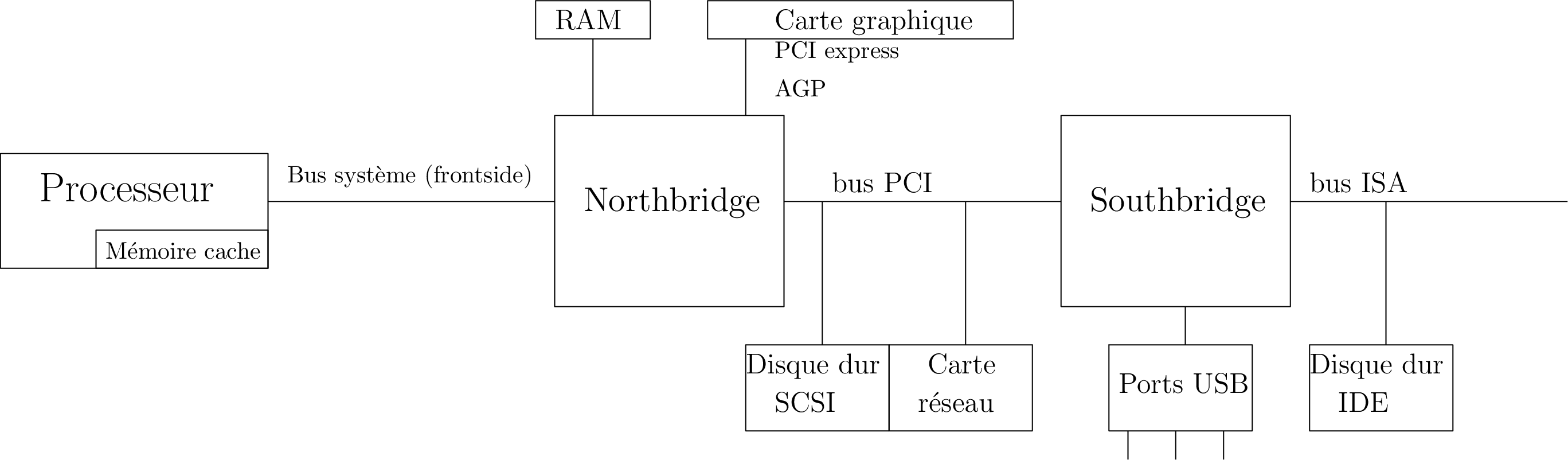

Les bus

| Bus | Largeur (bits) | Clk (MHz) | Débit (Mo/s) | Année |

|---|---|---|---|---|

| ISA 16 | 16 | 8.33 | 15.9 | 1984 |

| PCI 32 | 32 | 33 | 125 | 1993 |

| AGP | 32 | 66 | 250 | 1997 |

| PCI-E 3 (x16) | 16 | 8000 | 16000 | 2011 |

Bus parallèles (échange de mots, large mais court) / Bus série (bit à bit, e.g. USB)

Comment contacter les entrées/sorties ?

Il faut pouvoir contacter les registres du contrôleur du périphérique.

Autre solution : pas de bus d’adresse; placer dans le message un identifiant du destinataire.

Comment discuter sur le bus ?

Protocoles d’échange : e.g. lecture mémoire

Fréquence d’horloge : ajustée au périphérique le plus lent

Protocoles d’échange : e.g. lecture mémoire

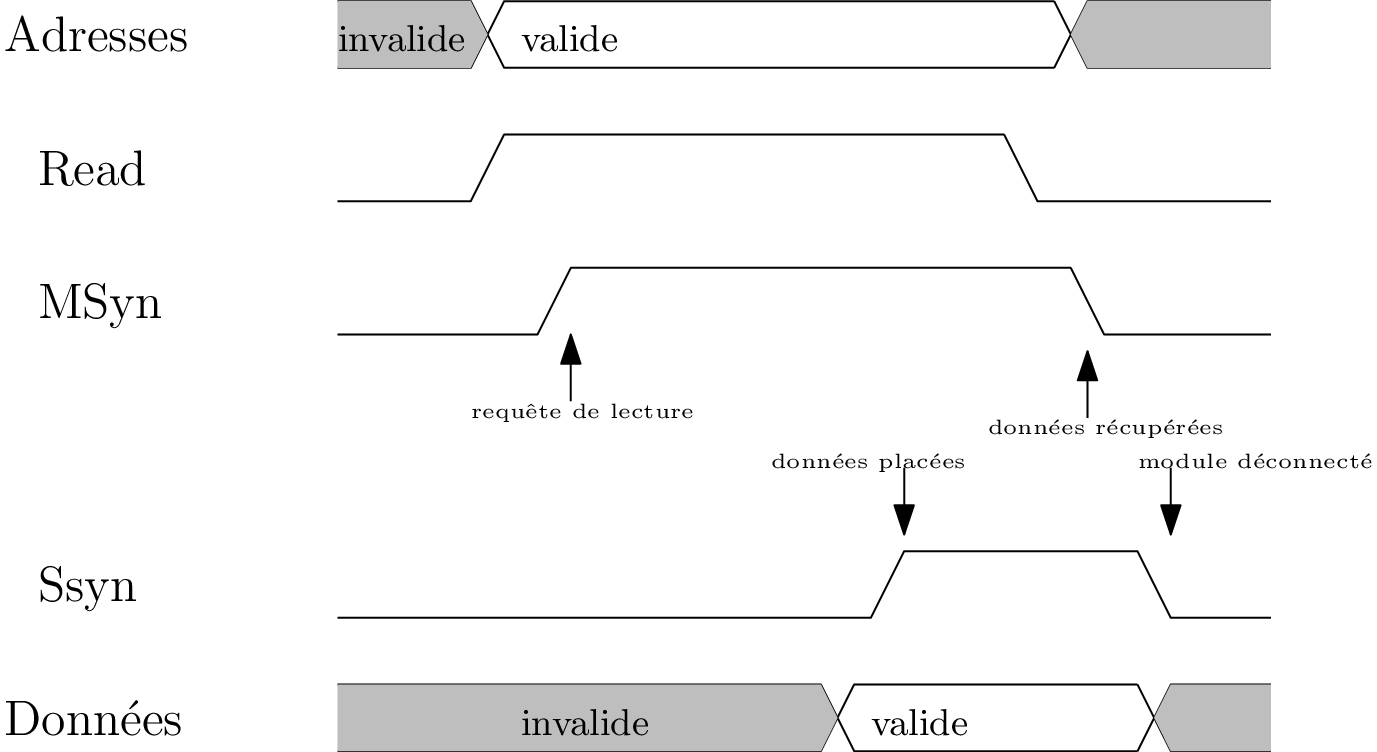

Pas d’horloge mais des signaux d’état : handshaking

Plus réactif mais plus compliqué à mettre en oeuvre.

Protocoles d’échange : e.g. lecture mémoire

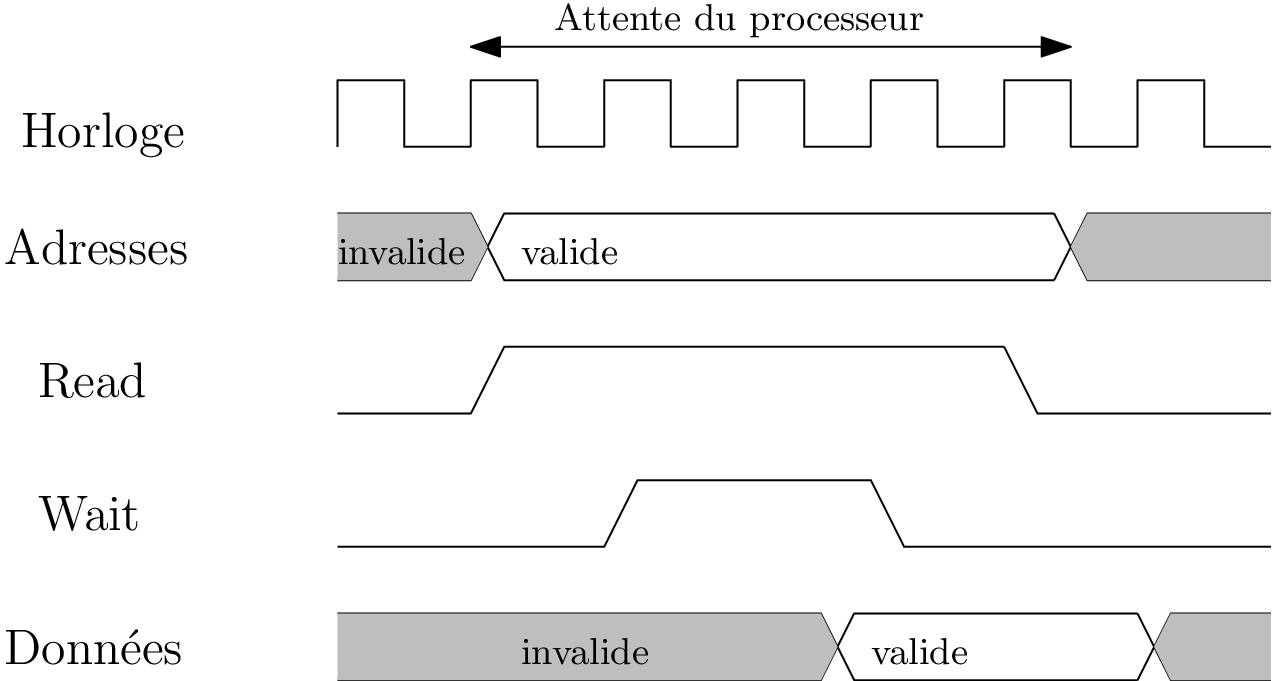

Attente ? e.g. Wait State : attente active

Et si on est plusieurs à vouloir parler ?

On sait :

- comment interconnecter un périphérique avec le chemin de données : bus

- comment réaliser un transfert synchrone/asynchrone

mais on a :

- “un” bus

- plusieurs acteurs : mémoires, périphériques, CPU, …

Nécessité d’arbitrer, e.g. le premier dans un certain ordre.

Et comment la demande d’échange avec le périphérique est prise en charge ?

Gestion des périphériques par interruption

Evènements synchrones

Déroutements (trap, exception): événements synchrones avec l’exécution d’un programme, liés à une erreur : division par zéro, overflow, accès invalide à la mémoire : e.g. stack overflow

Ex : Overflow

Comment prendre en charge des débordements lors d’opérations arithmétiques ?

- le programme teste, après “chaque” opération, le bit overflow (Status register)

- programme plus long en mémoire et à l’exécution et plus compliqué à écrire

- dérouter le fil d’exécution si un débordement a lieu (à la JZA); pas de surcoût !

Au regard d’un programme, on peut prévoir quand un déroutement peut avoir lieu.

Interruptions : Evènements asynchrones

Evènements asynchrones; e.g. appui sur un bouton, une touche de clavier, bourrage papier, lecture mémoire terminée, …

Prise en charge par scrutation

On interroge régulièrement le périphérique

- programmation explicite

- surcoût à l’exécution

Prise en charge par interruption

Ecoute passive du périphérique : exécute un programme particulier que lorsque le périphérique lève une demande d’interruption

→ sollicite moins le processeur (e.g. lecture sur disque : données prêtes)

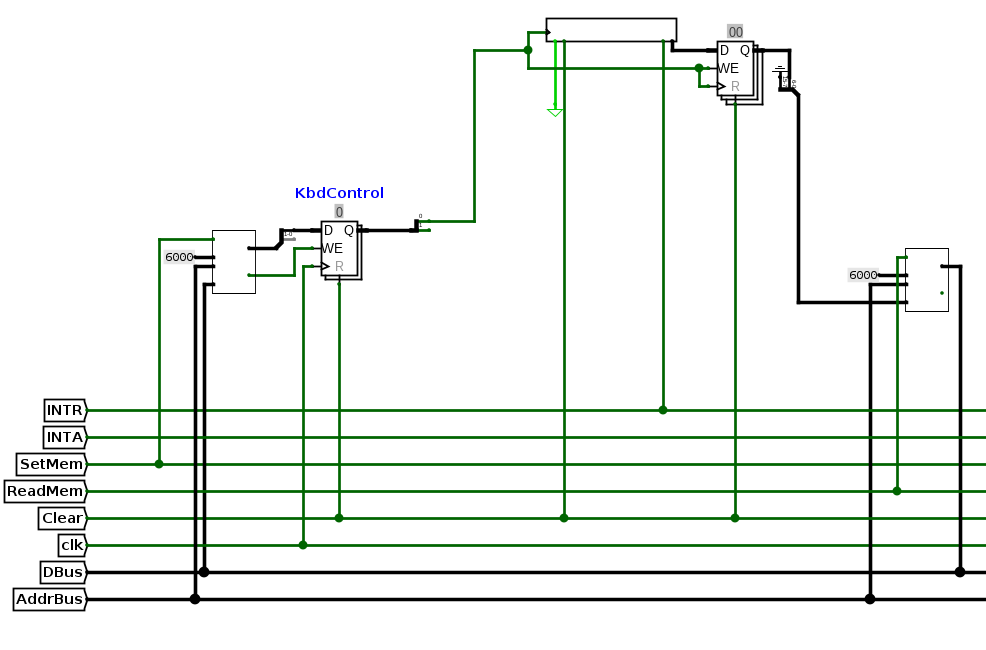

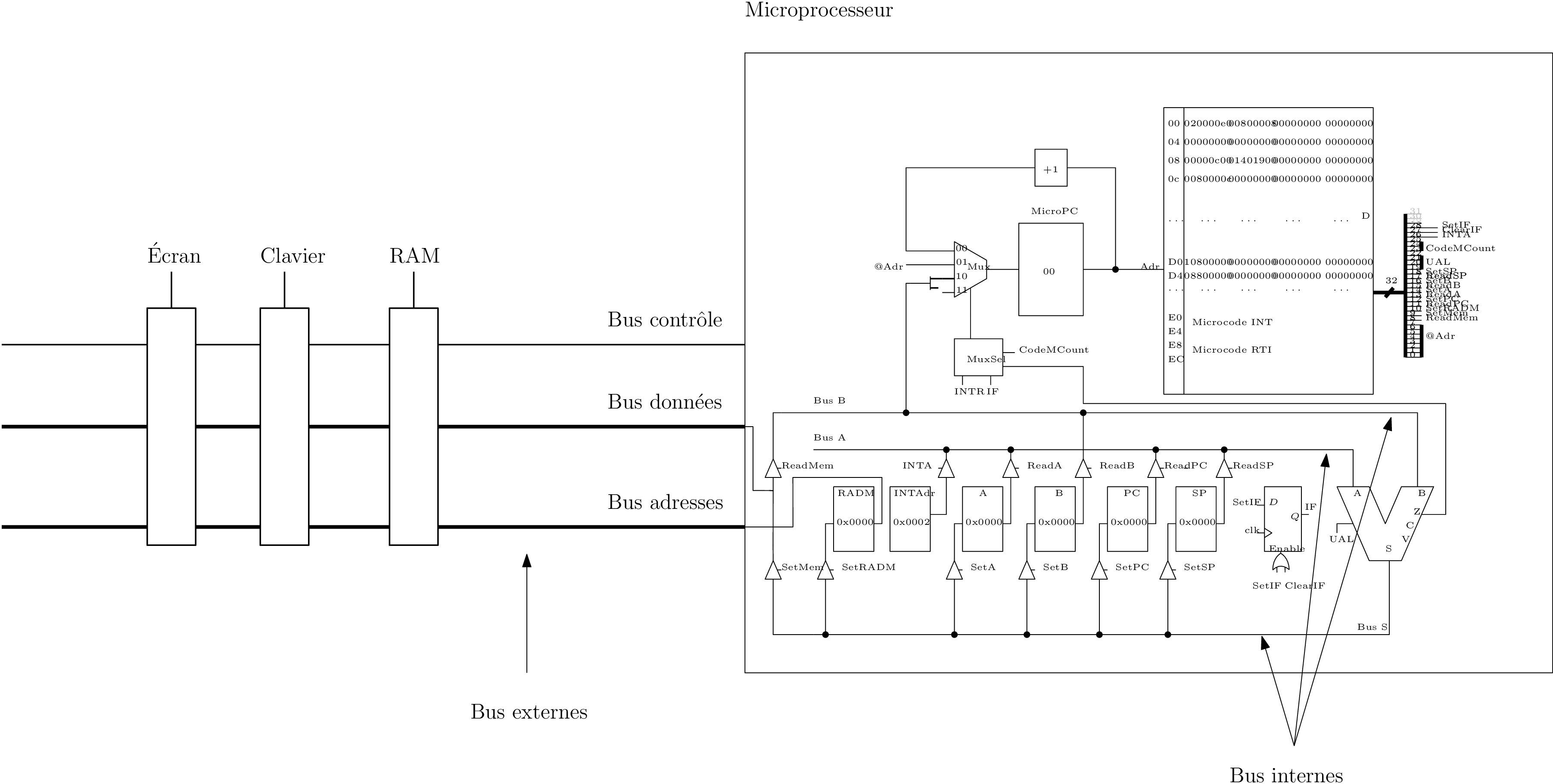

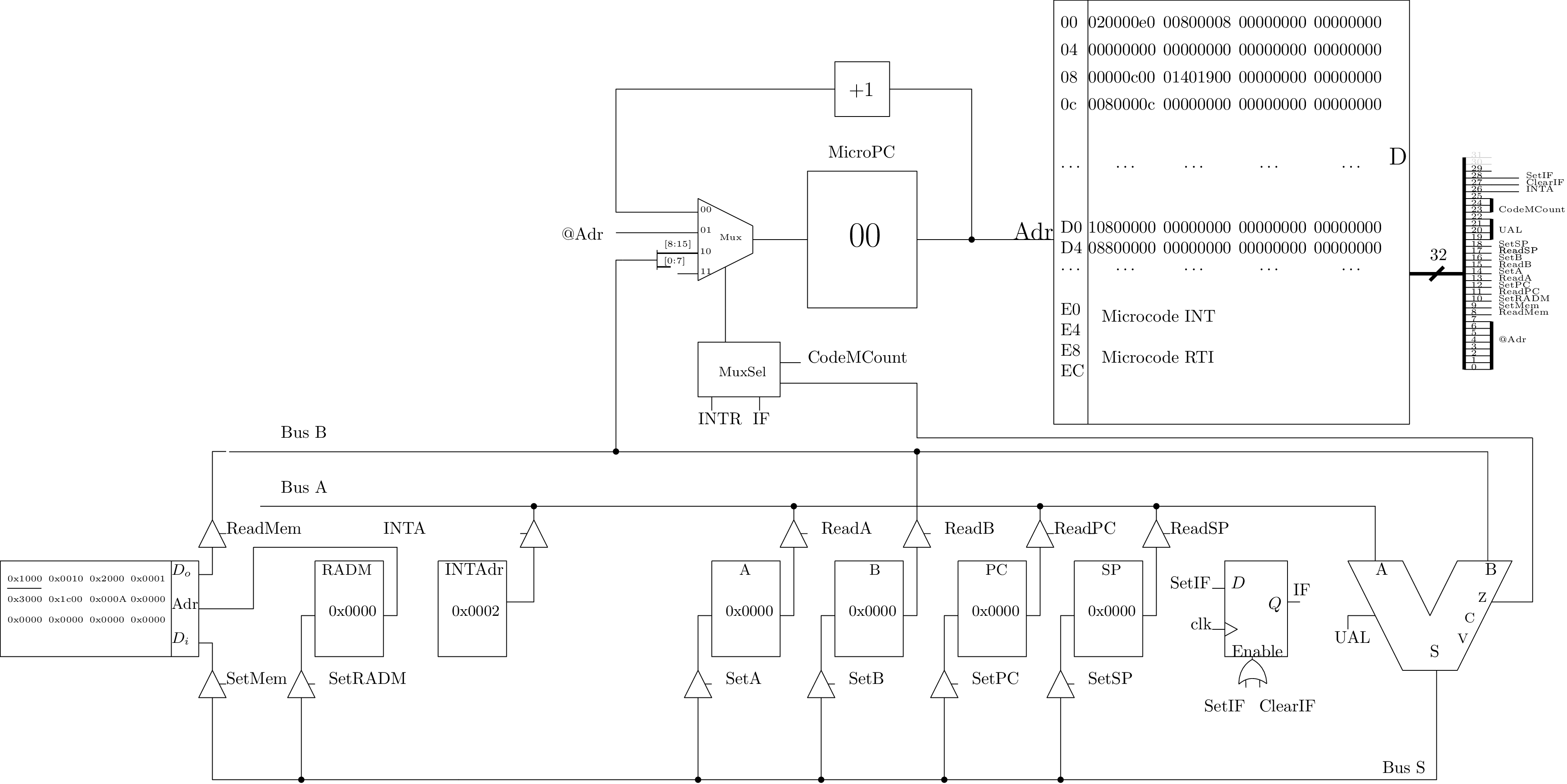

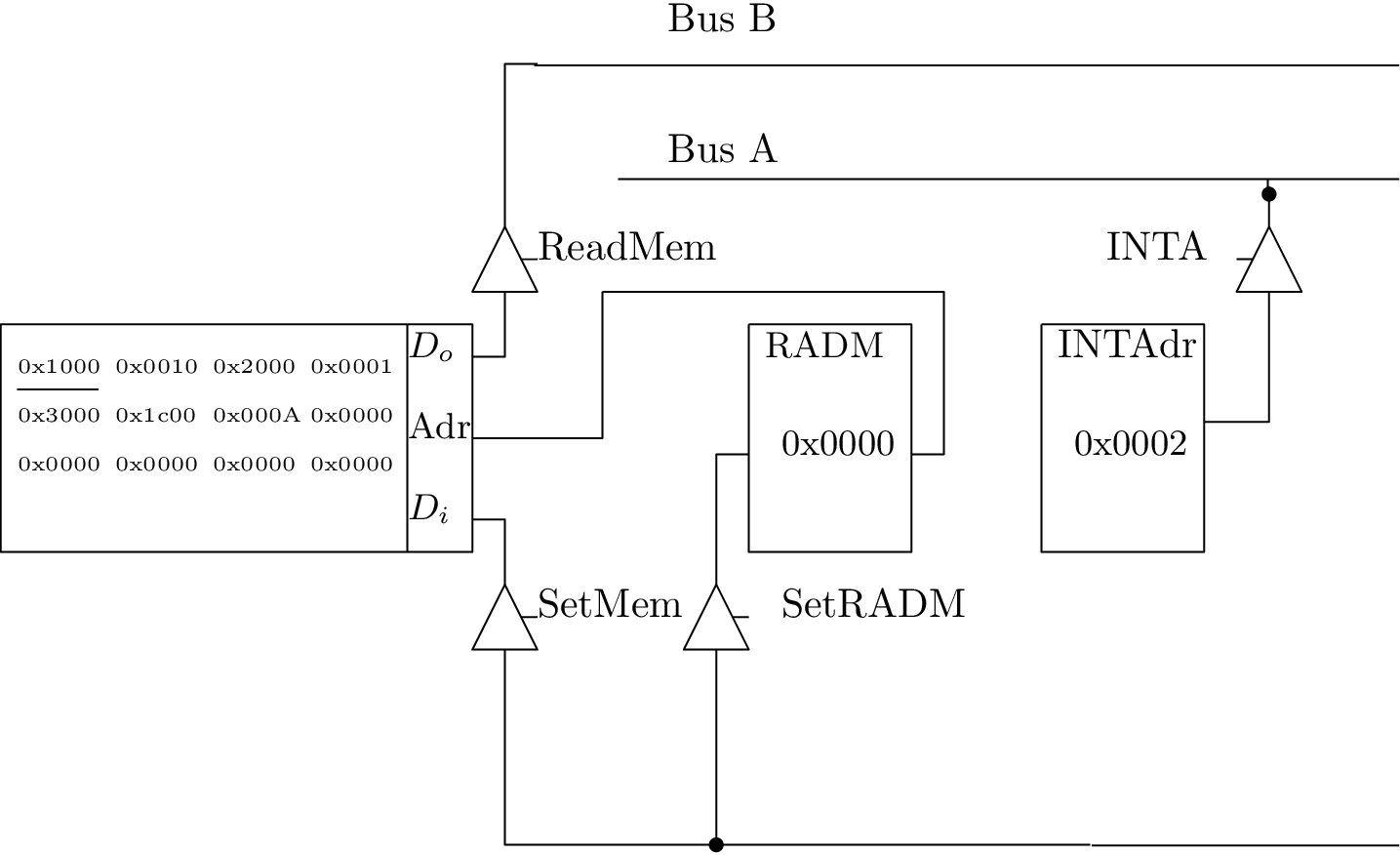

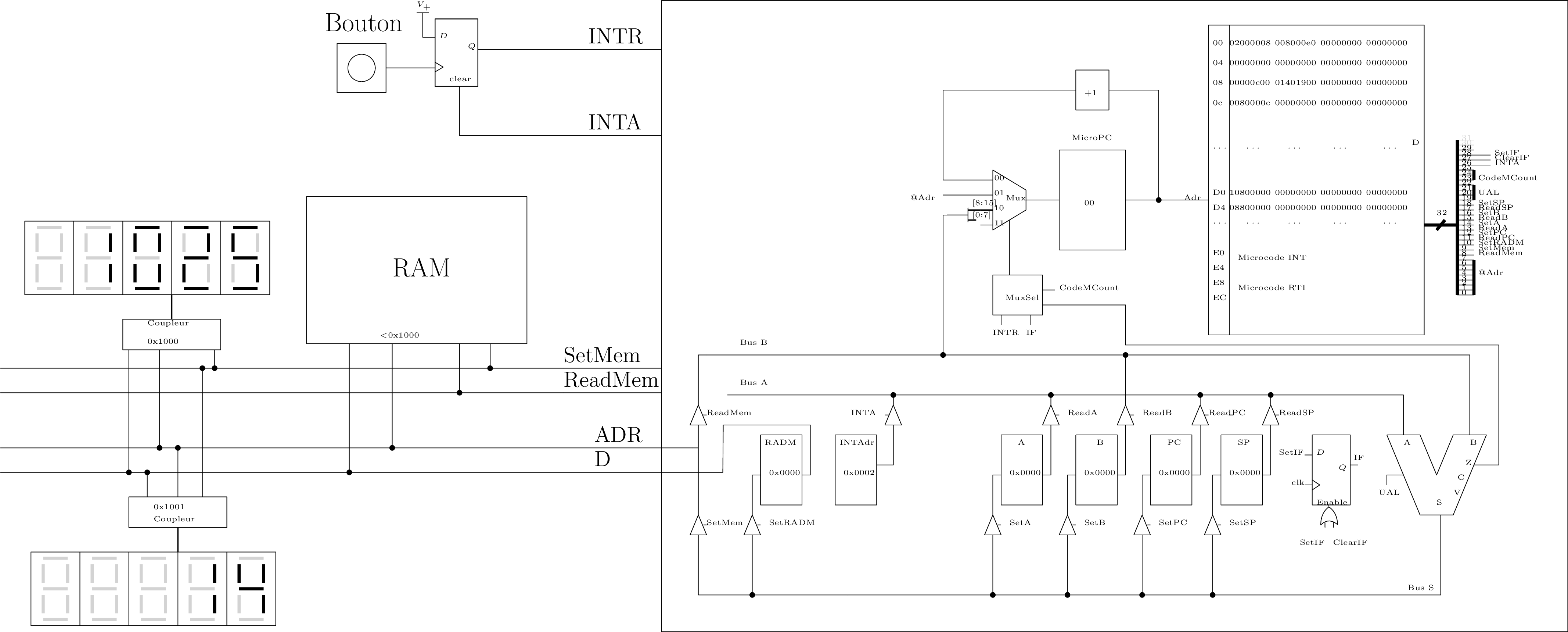

Modification du chemin de données

On ajoute une ligne de requête d’interruption (INTR) qu’un périphérique peut mettre à l’état haut. Registre IF pour y être sensible ou non.

Ecoute passive des demandes d’interruption

Avant le fetch/decode, on teste si une demande d’interruption est levée :

- si oui, on part en interruption

- sinon, on entre dans la phase de fetch/decode et exécution de l’instruction, comme d’habitude

| CodeMCount | Z | INTR & IF | \(S_1S_0\) | Sémantique |

|---|---|---|---|---|

| 000 | - | - | 00 | MicroPC := MicroPC+1 |

| 001 | - | - | 01 | MicroPC := @Adr |

| 010 | - | - | 10 | MicroPC := Instruction |

| 011 | 0 | - | 00 | MicroPC := MicroPC+1 si \(S≠0\) |

| 011 | 1 | - | 01 | MicroPC := @Adr si \(S=0\) |

| 100 | - | 0 | 01 | MicroPC := @Adr si \(\overline{INTR \& IF}\) |

| 100 | - | 1 | 00 | MicroPC := MicroPC+1 si \(INTR \& IF\) |

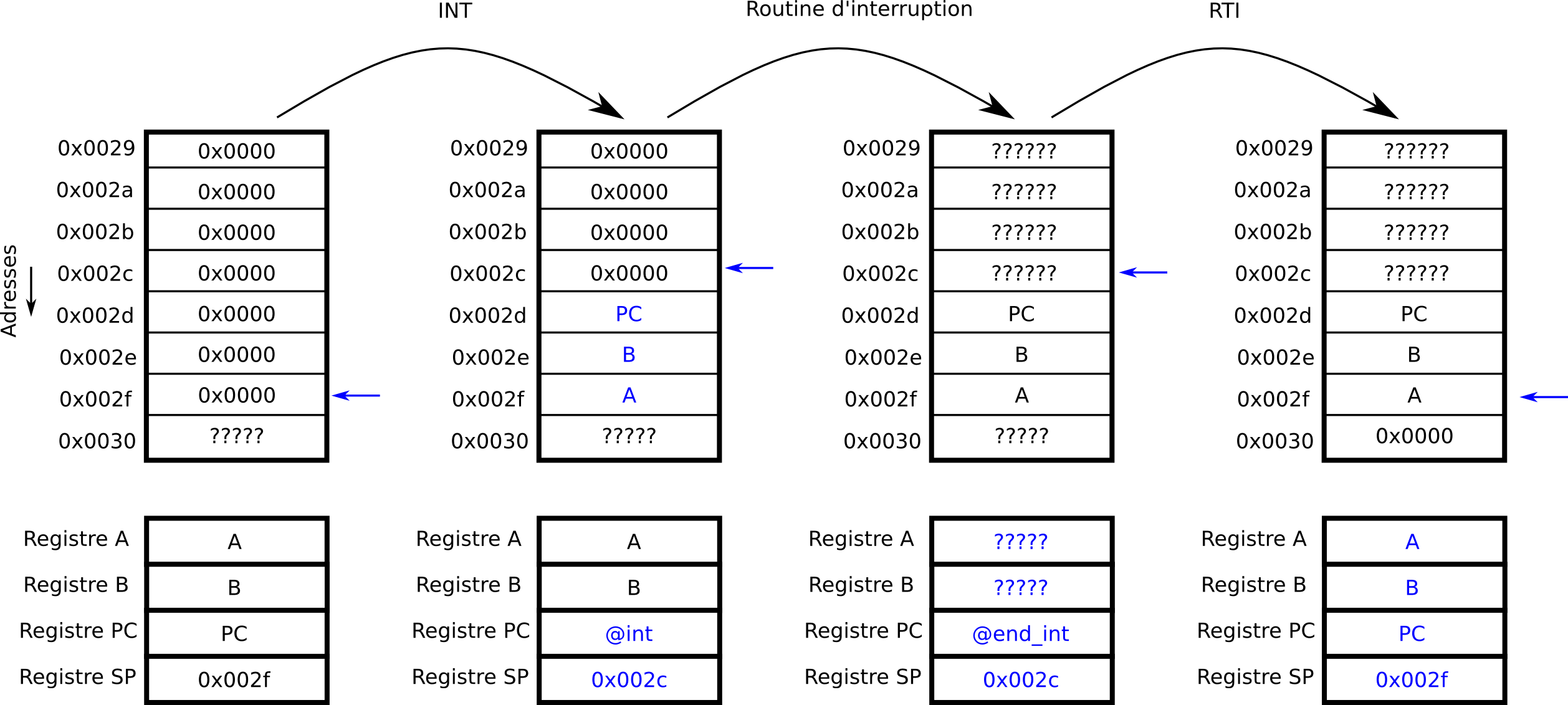

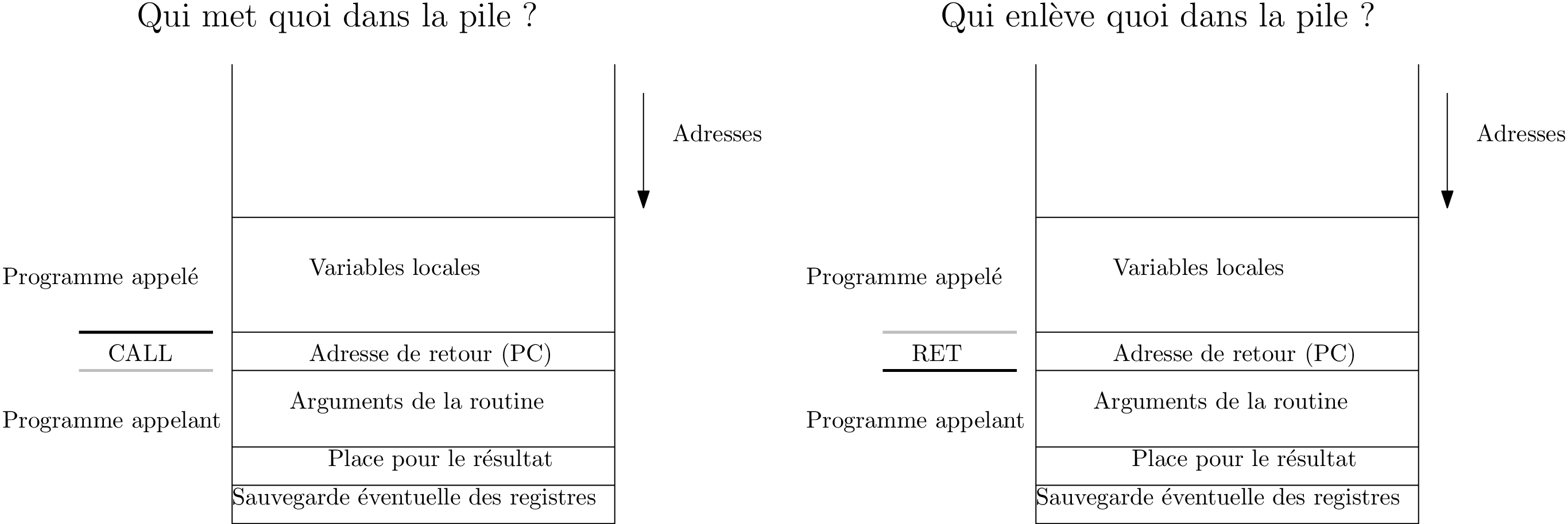

Prise en charge de la demande d’interruption

Principe

L’interruption doit être gérée de manière transparente pour le programme interrompu

⇒ sauvegarde du contexte d’exécution (sur la pile)

Nouvelles instructions

- INT (0xE000) : partir en interruption :

- sauvegarde du contexte d’exécution sur la pile

- chargement de l’adresse du programme d’interruption

- RTI (0xE800): revenir d’une interruption :

- restauration du contexte d’exécution du programme interrompu

- STI (0xD400) : démasque les interruptions : IF := 1

- CLI (0xD000) : Masque les interruptions : IF := 0

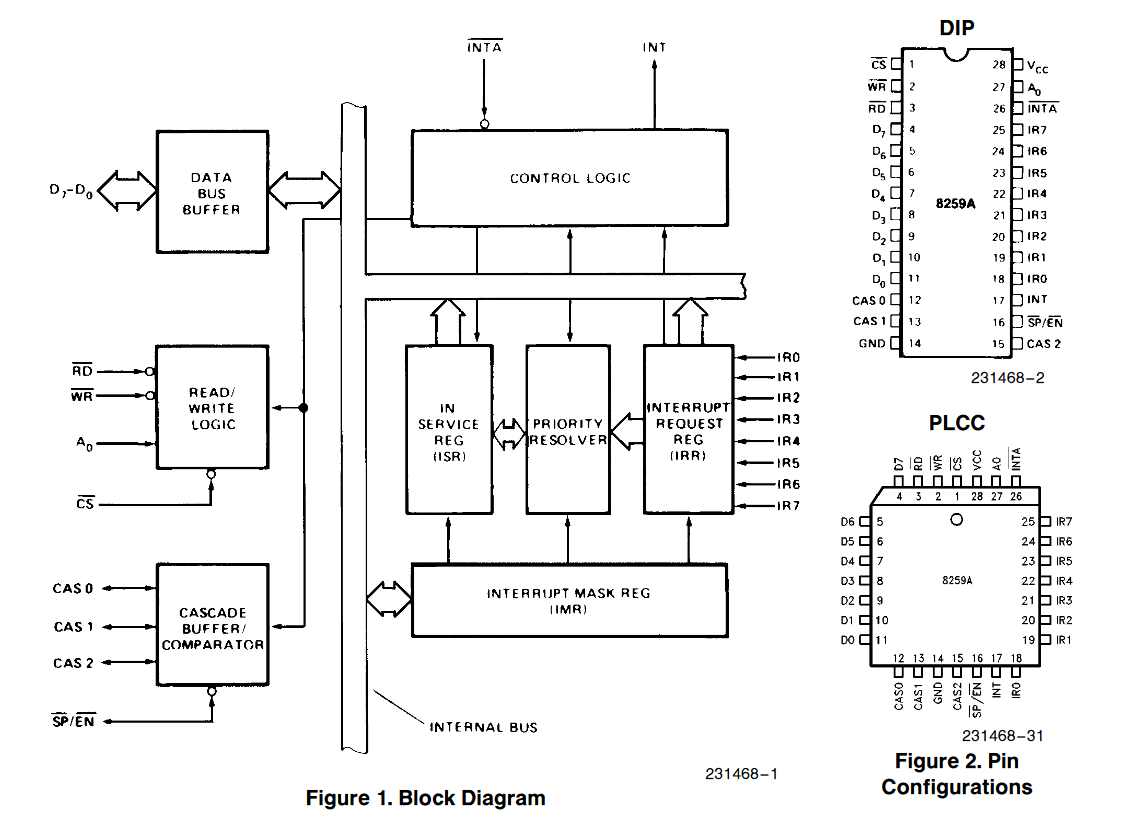

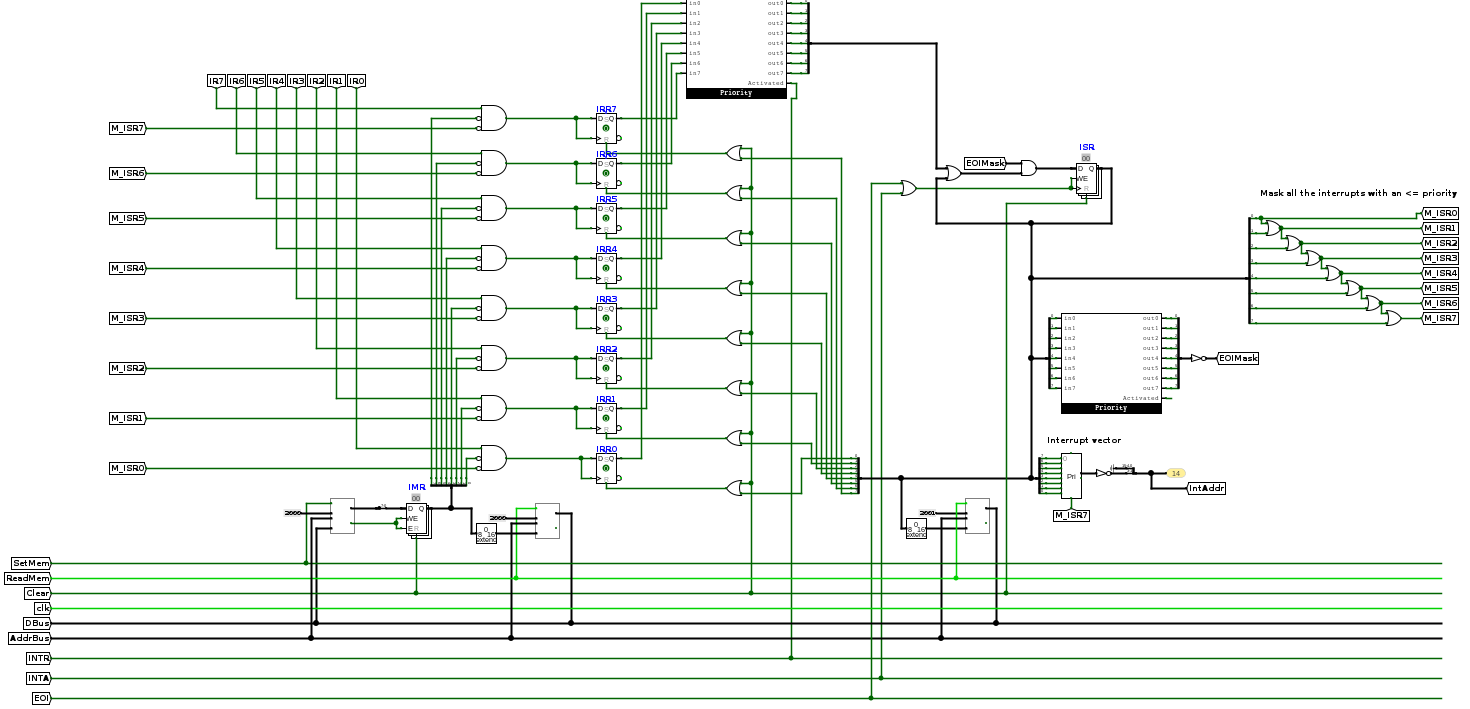

Comment savoir quel programme exécuter en cas d’interruptions

Vecteur d’interruption : programme à exécuter en cas d’interruption

On stocke une table des vecteurs d’interruption en mémoire. Une adresse, placée sur le bus, permet d’adresser la bonne routine.

Chez nous : une seule interruption

Pour le moment, avec une seule interruption, l’adresse de la routine d’interruption est codée en dur, dans le registre INTAdr

Résumons

- le périphérique lève une requête d’interruption INTR=1

- le processeur détecte la requête

- le processeur sauvegarde l’état courant et se branche sur la routine d’interruption (vecteur d’interruption ou interrupt handler)

- le processeur accuse réception

- le processeur restaure l’état

Attention

La gestion de l’interruption implique la pile !!

⇒ Phase d’initialisation (JMP init) minimale : 1. par défaut IF = 0 2. LDSPI … 3. STI

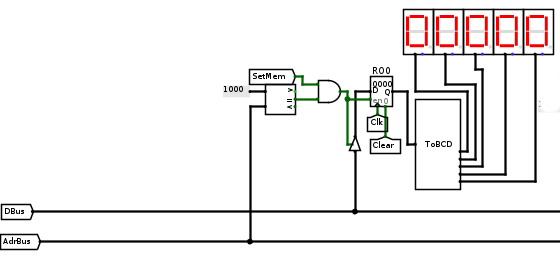

Exemple jouet : En TP

Plusieurs interruptions ?

On s’est limité pour le moment à un seul périphérique.

Petits pas vers l’OS : Ordonnanceur

Problème

Comment exécuter plusieurs programmes “en même temps” :

- avec plusieurs chemins de données (architectures multi-coeurs)

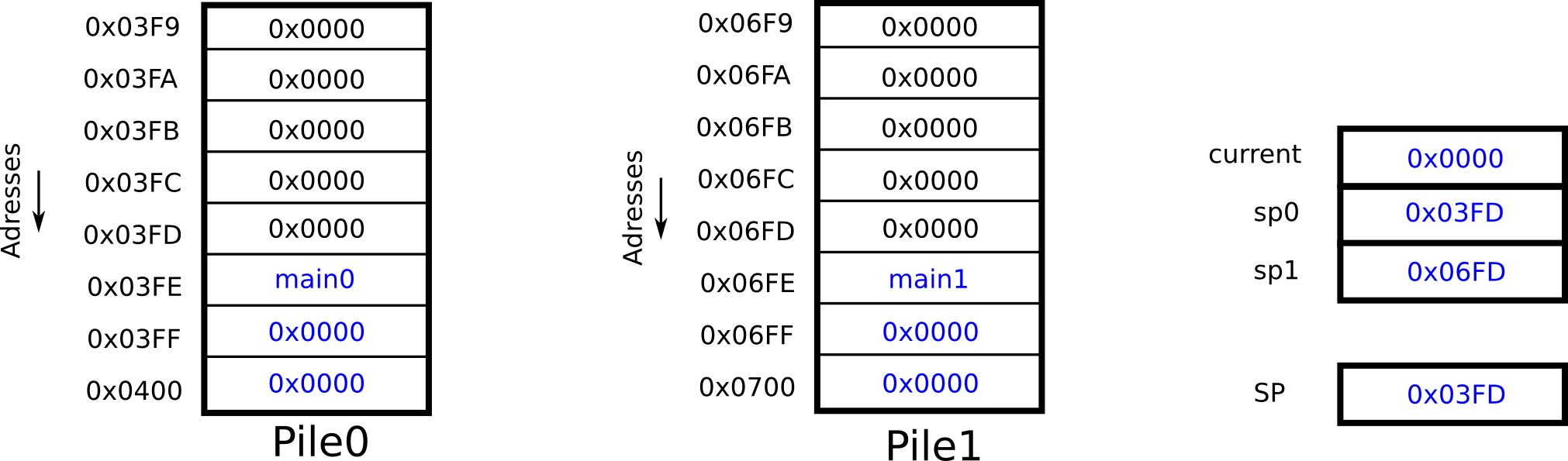

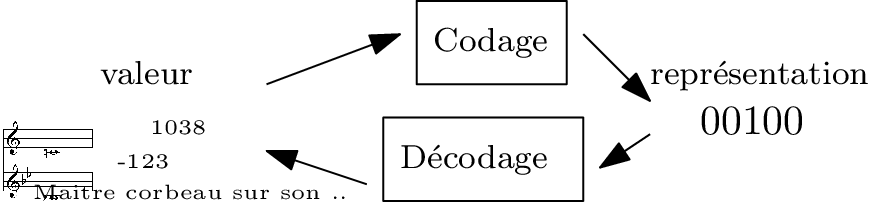

- avec un seul chemin de données partagé par deux programmes : en TP et un basculement de contexte régulier (interruption d’un timer)

Basculement de contexte

Rétrospective et conclusion

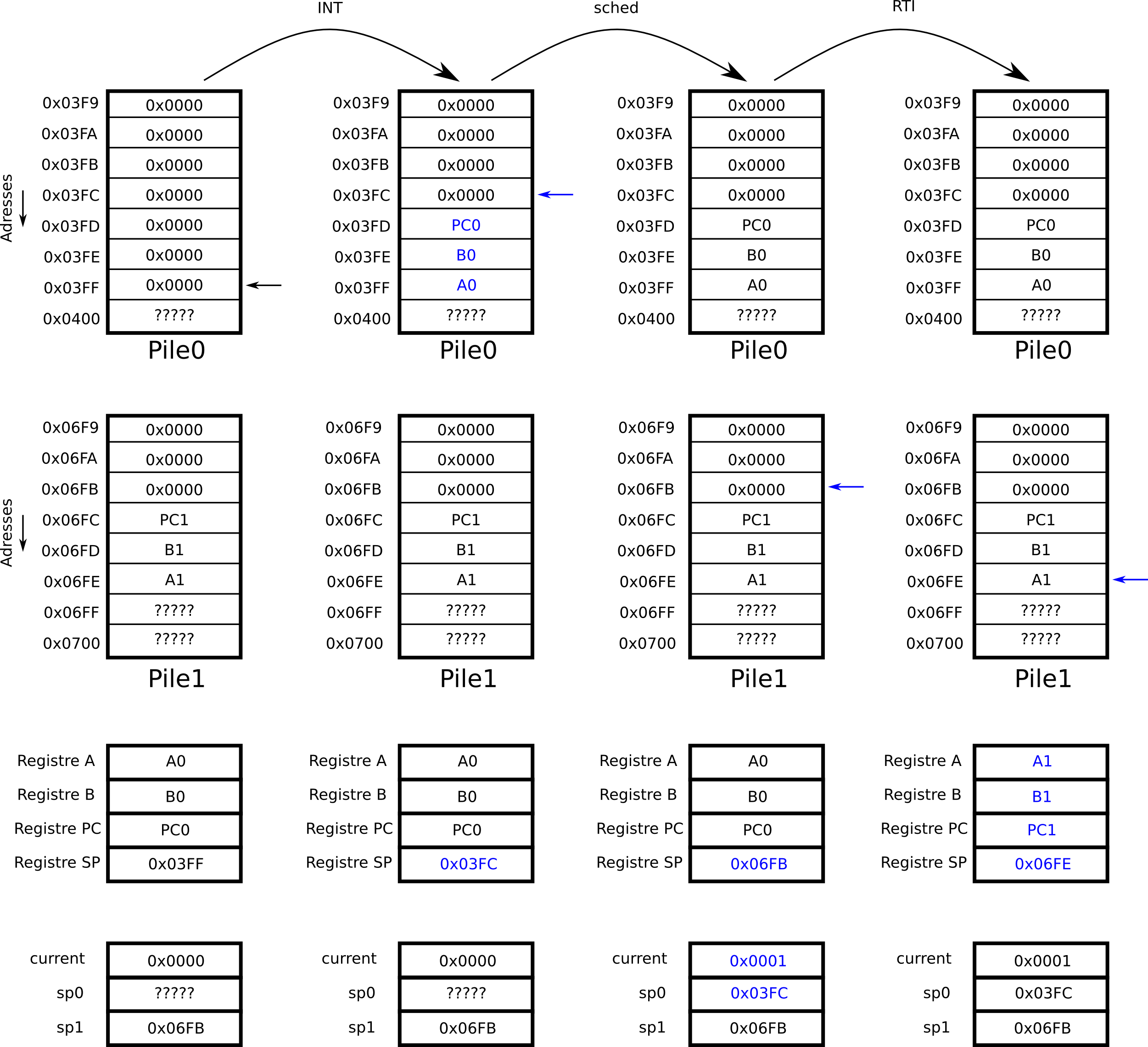

Cours 1 : Codons tout en binaire

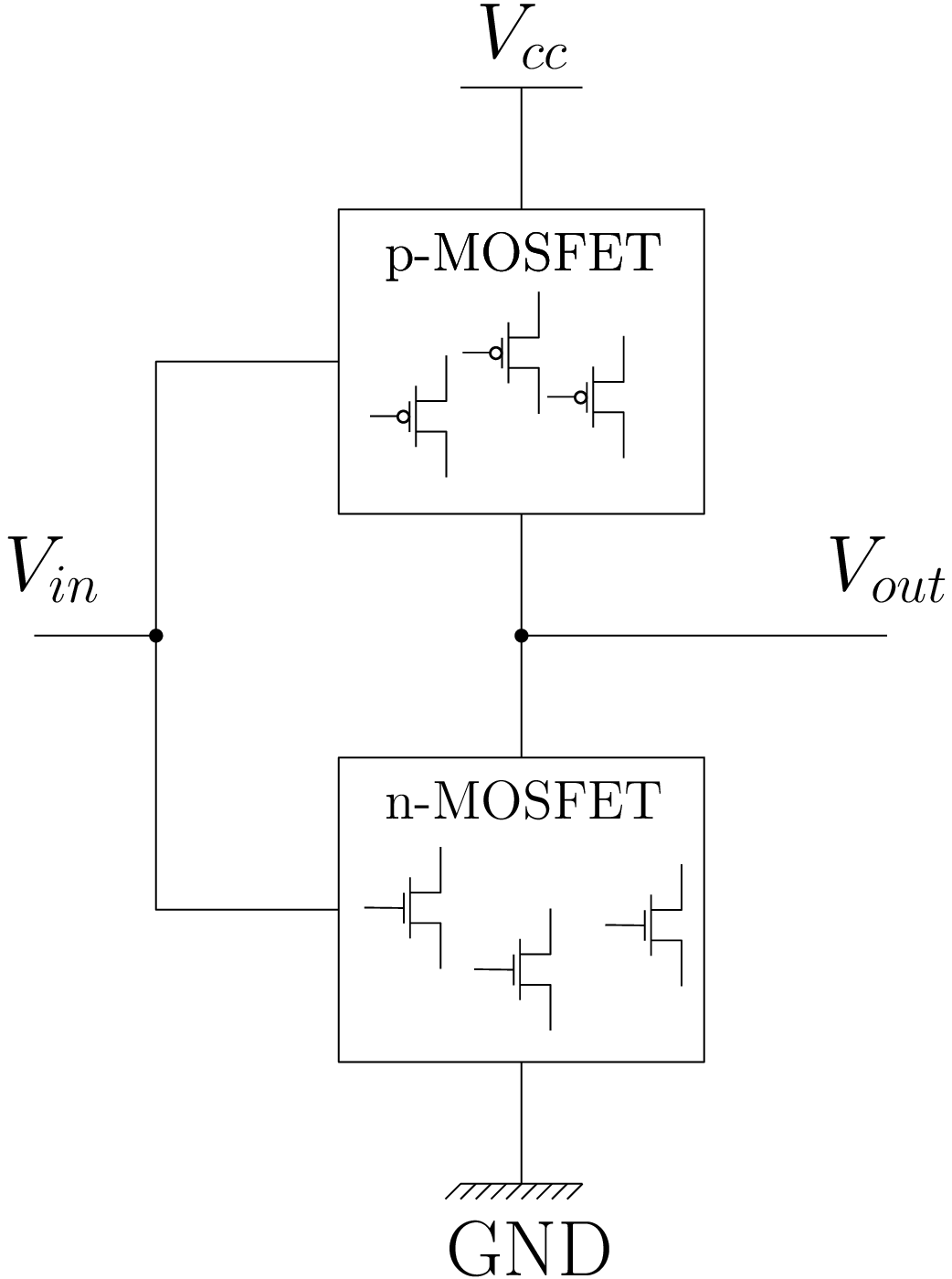

Cours 2-3 : Transistors, Circuits logiques, séquenceur

Cours 4-5 : pile et programmation

Programmation

⇒ Ouverture vers la programmation (C++, etc..)

Cours 6 : mémoires caches

Cours 7 : périphériques et interruptions

Produced with quarto

Comment exploiter les principes de localité ?

Solution 1) A la charge du programmeur

→ Pas très pratique…

Solution 2) Hierarchie de mémoires

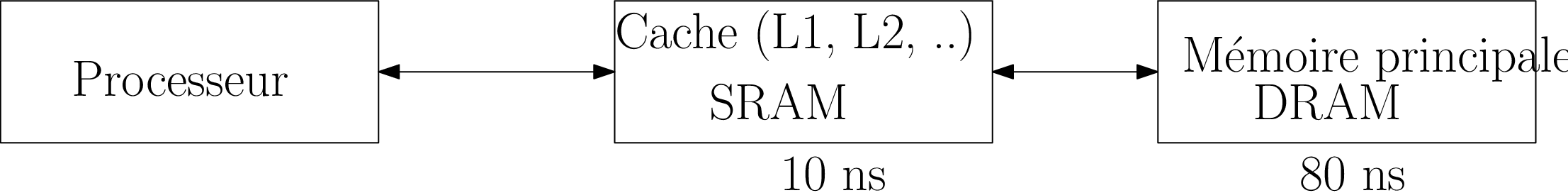

Performances du cache

Temps moyen d’accès mémoire \(T_m \approx HR. t_{cache} + MR. t_{mem}\)

Pour \(HR = 90\%\) : \(T_m = 17 ns\).